Интегратор

Иллюстрации

Показать всеРеферат

...! t:нт но-1 < ., :i. еск (библиотек М

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Счоз Советских

Социалистических

Респубпик (11) 542200 (61) Дополнительное к авт. свид-ву— (22) Заявлено 07.07.75 (21) 2153648/24 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано05.01,77.Бюллетень ¹ y (45} Дата опубликования описания 30. 03. 77 (51) М. Кл. G 06 5 7/18

Гасударственный комитет

Саввта Министрав СССР па делам иэабретений и открытий (53) УДК

6 81. 335 (08 8. 8) (72) Авторы изобретения

А. M. Косолапов и В. П, Сенников

Куйбышевский политехнический институт им, B.Â. Куйбышева (71) Заявитель (54) ИНТЕГРАТОР

Изобретение относится к вычислительной и измерительной технике, может быть использовано также в различных устройствах автоматики для интегрирования медленно меняющихся сигналов, Известен интегратор (11, содержащий блоки интегрирования, сравниваюшие устройства, переключатели, счетчик, сумматор. Однако такой интегратор обладает недостаточной точностью.

Наиболее близок к предлагаемому интегратор (2j, содержащий интегрирую щие блоки на усилителях постоянного тока с конденсатором в цепи обратной связи, ключи, блок управления, выходы которого соединены с управляюшими входами ключей, сумматор, выход которого является выходом интегратора; входы интегрирующих блоков через два масштабных резистора подключены ко входу интегратора.

В этом интеграторе входные интегрирующие усилители, работаюшие попеременно, вместе с полезным входным сигналом интегрируют дрейфовые токи и напряжения

2 усилителей постоянного тока (УПТ). Ошибка от дрейфа нуля УПТ особенно велика при интегрировании медленно меняющихся сигналов малой величины.

Цепь изобретения — lIoBbfIIleHHe точности интегрирования медленно меняюшихся сигналов.

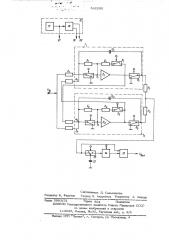

Предлагаемый интегратор отличается тем, что в него дополнительно введены масштабные резисторы, переключатель, запоминающий блок, дозируюший конденсатор, причем в каждом бпоке интегрирования первый ключ включен между входом усилителя постоянного тока и одной обкпадкой конI денсатора, второй - между выходом усилителя постоянного тока и другой обкладкой конденсатора, вход усилителя постояннного тока через последовательно соединенные первый дополнительно введенный мас20 штабный резистор и третий ключ соединен с выходом, усилителя постоянного тока, и через второй дополнительный масштабный резистор — с суммирующим входом интегрирующего блока; выход усилителя

25 постоянного тока первого блока интегрирова542200 ния через третий дополнительный масштабный резистор соединен со входом второго блока интегрирования, выход усилителя постоянного тока второго блока интегрирования через четвертый дополнительный масштабный резистор — co входом первого блока интегрирования; выходы первого и второго интегрирукпцнх блоков объединены и соединены с первым вхэдэм сумматора и с Одним неподвижным контактом допэлнительно введенного переключателя, другой неподвижный контакт которого соединен со входом запоминающего блока. Выход последнего связан со вторым входом сумматора а управпяюший вход запоминаюшего I5 блока подключен к вь|ходу блока управления.

Подвижный контакт дополнительно введенного переключателя соединен с Одной обкладкой дозируюшего конденсатора другая обкладка которого соодинена с шиной ну лево- 20

ro потенциала, На чертеже приведена схема устройстИнтегратор содержит интегрируюшие лОки 11 1 1 1 усилители Iioc70FHEIol О ToKQ 75 (УПТ) 2,1, 2,масштабные резисторы 31,. (10 ., выходные резисторы интегрирующих блоков 1 1,. 1 1, переключатель 1 2, до- 30 зируюший конденсатор 13, запоминаюший блок 14, сумматор 15, блок управления

16, содержащий мультивибратор 17 и триггер 18, Устройство работает следуюшим образом.

Блок управления 16 с помошью мультивибратора 17 и триггера 18 формирует на выходах 19, 20 сигналы одинаковой длительности, которые управляют кпк>чами 71, 72, 8.1, 8?, 9, 9, а сигнал с выхода 21 управляет переключателем 12 и запоминающим блоком 14. Сигнал с выхода 19 переводит ключи 7, 8.1 первого интегрирующего блока в верхнее положение, а ключ 9у размыкает. В ето же время сигнала на выходе 20 нет, и ключи 7?

8 второго интегрируюшего блока остаются в нижнем положении, а ключ 92 замк50 нут, При таком состоянии ключей напряжение на выходе TILT второго интегрирующего блока пропорционально напряжению дрейфа нуля усилителя, величина которого определяется соотношением масштабируюших резисторов 51, 6?. Зто напряжение через резистор 4 поступает на суммируюший вход первого интегрирующего блока, работаюшего в режиме интегрирования. Напря?кение на выходе первого интегрируюшего блока пропорциОпально и11тегрдлы10ь з13а" ени10 от суммы напряжения вхо=.ного си1.-пала, дрейфа нуля УПТ второго интегриру10шего блока, а также дрейфа пуля собственНог o УПТ. Через резистор 11 выходное напряжение первого цнтегри у:оп его бло.ка поступает сдповремеп;ю на сумматор

15 и через 11ерекпю:атал = 12- на:озиру-юший конденсатор 1 3.

Сигнал с мультивибратора 17 блока управления 6 переводит три»1 cp - 8 в другое положение, и при етом. на выходе

20 появпястся управляющий сигнал, который переключает кп очи 7; . 8 ° второго . 1 интегрирующего блока в верхнее попожсEIHe а KHIÎH 9) размь(Qe, N I»0 IH 7, 81 первого интегрирую шег с бп01;а юоз1:рац1аЮТСЯ B НИжнее по тО?11011ИЕ, КП10- = r 1аЬ1ЫКа» ется. Конденсатор 1 0 Iepeз ключи,, 8, обнуляется, а выходное напряжение с У I!T через резистор 4, посту» (т -1» су-, »,.1ир;-=Г

ЮЩИй ВХОД ВТОРОГО iiПТОГЮ»n",r,»lieÃO ОПОКа которь:й интегрирует входной сигнал, дрейф нуля собстве1шого TI IT Ii 11апря?ке 1ие, пропорциональное дрсйфу гуля УГ 1ервого интегрирующего блока.

Сигнал малой дп11т-:i .10:-.. 1 с у.1:-т.1вибратора 17 . 007у i= сот с ?1сд: 21»а перекпючател1 1 2,1 лэд л Оч .От,;Озию :с-1ппй конденсатор 1 3 ко L?»O.Ió за .01, и1?а10шего OllOKG 14, I1рн;:.то L. сэме»т перскиоченпЯ УРов01:: — =.II,H?:.0. II H»а в:?loge нос педнегс Ilp 0»op ш10напе!1 п11-эг р алу OT входного ст иа-.»а» «»аки1» Ос;,азс,. за оди: цикл п»тегр?цроваиы, n;-,.;,0»010:;<: : .; себя работу пергого и второго "1. 01 рирук»иих тов ицтегрирова пьч ." блоке = ...:апря?ке11ие

Г иа выходе послед»е- -0 1..» ссотв-.òo:Hó1ошем масштабе пропорц11011аль110 и». 01 рап 110...1у значеиц0 oт вход110гс с.:1г1)r»!o, »0 без дрейфа нуля входных л»тегрируюц1их блоков.

Действительно, за полнь1й цикл интегрирования дрейф нуля первогo интегрируюшего блока, как и второгс интегрируется дважды .

/ один раз собствонным иптегрпруюшцм блоком, а за вторую половину цикла — другим интегрируюшим блоком, нс с обратным зчаком. Принимая во в11ик.ание, Izo за один цикл интегрирова1п1Я дрейф нуля интегрируюших блоков меняется весьма мапо, подбором резисторов 5, 6, 4 ; 5?, 6, 4? можно доб итьс я, чтобы су мма н апря же ний, пропорционапьчых интегралу от дрейфа нуля интегрируюших б".îêîâ. равнялась нулю.

Использование в дан1,ом устройстве новых элементов и связей позволяет при интегрировании медленно меняюшихся сигналов уменьшить погренность от дрейфа

542200 нуля усилителей постоянного тока входных блоков интегрирования, снизить требования к УПТ. Устройство может быть легко выполнено методами интеграпьной технопогии.

Формула изобретения

Интегратор, содержащий интегрирую- 10 шие блоки на усилителях постоянного тока с конденсатором в цели обратной связи, ключи, блок управления, выходы которого соединены с управляющими входами ключей, сумматор, выход которого явпяется выхо- д дом интегратора, входы интегрирующих блоков через два масштабных резистора подкпючены ко входу интегратора, о т и ич аю щи йс я тем, что, с цепьюповышения точности интегрирования, в него 20 введены дополнитепьные масштабные резисторы, переключатель, запоминающий блок, дозирующий конденсатор, причем в каждом интегрирующем блоке первый кпюч включен между входом усипителя Л постоянного тока с одной обкладкой конденсатора, второй — между выходом усилитепя постоянного тока и другой обкладкой конденсатора, вход усилителя постоянного тока через последовательно соединенные первый дополнительно введенный масштабный резистор и третий ключ соединен с выходом у-силителя постоянного тока и через второй допопнитепьный масштабный резистор — с суммирующим входом интегрирующего блока, выход усилителя постоянного тока первого интегрирующего блока через третий допопнитепьный масштабный резистор соединен со входом второго интегрирующего блока, выход усилителя постоянного тока второго интегрирующего блока через четвертый дополнительный масштабный резистор — co входом первого интегриру юшего блока, выходы первого и второго интегрирующих блоков эбьединены и соединены с первым входом сумматора и с одним неподвижным контактом дополнительно введенного переключателя другой неподвижный контакт которого соединен со входом запоминающего блока выход последнего связан со вторым входом сумматора, а управляющий вход запоминающего блока подключен к выходу блока управпения, подвпжчый контакт дополнительно введенного переключателя соединен с одной обкладкой дозируюшего конденсатора, другая обкладка которого соединена с шиной нупевсго потенциала.

Источники информации, принятые Во внимание при экспертизе:

1, Авторское свидетельство, 4 3017 13, f06 G 77//1188, 28.11.69.

2 Смолов В. Б. Анапоговые вычислительные машины, изд. "Высшая школа", Москва, 1972, стр. 179.

542200

1

l

З

I

I !

Я т 1

С оставитель й. Снимшикова

Редактор Б, Федотов Техред Н. Андрейчук Корректор А. Лакнда

Заказ 5983/31 Тираж 864 Подписное

ЫНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4