Запоминающее устройство с одновременной выборкой нескольких слов

Иллюстрации

Показать всеРеферат

Р 1 (ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистимеских

Республик (и) 542241 (61) Дополнительное к авт. свнд-ву (22) Заявлено02.10.75 (21) 2177514/24 с присоединением заявки № (23) Приоритет (43) Опубликовано 05.01.77,Бюллетень № 1 (45) Дата опубликования описания30.03.77 (51) М. Кл."Ст 11 С 11/ОО

Государственный комитет

Совета Министров СССР по делам изобретений н открытий (53) УДК 681.327..6 (088.8) А. А. Молдованов, Ф. В. Фролов, М. Н. Шнайдер и Л. E. Яшук (72) Авторы изобретения

Одесский электротехнический институт связи (71) Заявитель им. А. С. Попова (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОДНОВРЕМЕННОЙ

ВЫБОРКОЙ НЕСКОЛЬКИХ СЛОВ

Изобретение относится к области запоминающихустройств ЗУ и может быть использовано, например, в читающих автоматах для распознавания образов.

Известны ЗУ с одновременной выборкой нескольких слов (1, 2).

Одно из известных устройств содержит регистры адреса, дешифраторы адреса, накопитель и логические элементы (1).

Недостатком этого устройства является ip небольшое количество одновременно выбираемых слов.

Наиболее близким техническим решением к данному изобретению является ЗУ с одновременной выборкой нескольких слов, 15 содержащее матрицу из ттт запоминающих элементов, адресный блок и т1 регистров направлений выборки (21.

Однако ЗУ не позволяет одновременно считывать даже два слова, если они не 20 расположены на одной диагонали матрицы.

Это снижает скорость работы устройства.

Белью изобретения является повышение быстродействия ЗУ.

Поставленная цель достигается тем, 25 чтэ предложенное ЗУ содержит 1l.тп элементов "И", первые входы которых подключены к выходам соответствующих запоминающих элементов, вторые — к выходам адресного блока, а выходы — к соответствующим входам регистров направлений выборки.

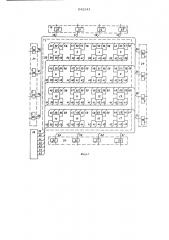

На фиг. 1 изображена функциональная схема ЗУ, содержащая матрицу, например, размером 4х4 и ячейки с одновременной выборкой слов по четырем направлениям: горизонтальному, вертикальному, диагональному растущему и диагональному падаюшему; на фиг. 2 — функциональная схема од ной ячейки матрицы ЗУ.

ЗУ содержит матрицу 1 с ячейками 2-1 7, адресный блок 18, регистр гэризонтального направления выборки 19, состоящий из триггеров 20-23, регистр вертикального направления выборки 24, состоящий из триггеров 25-28, регистр диагонального растущего направления выборки 29, состоящий из триггеров 30-33, и регистр диагонального падающего напряжения выборки 34, состоящий из триггеров 35-38.

542241

Выход 39 адресного блока 18 соединен с первыми входами ячеек 2-5, вторыми входами ячеек 2, 6, 10, 14, третьим входом ячейки 2 и четвертым входом ячейки

5, выход 40 — с первыми входами ячеек

6-9, вторыми входами ячеек 3, 7, 11 и

15, третьими входами ячеек 6,3 и четвертыми входами ячеек 4,9, выход 41 — с первыми входами ячеек lO-13, вторыми входами ячеек 4, 8, 12 и 16, третьими 1О входами ячеек 10,7 и 4 и четвертыми входами ячеек 3, 8, и 13, выход 42 — с первыми входами ячеек 14-17, вторыми входами ячеек 5, 9, 1 3 и 1 7, третьими вх одами ячеек 14, ll, 8 и 5 и четвертыми !5 входами ячеек 2, 7, 12 и 17, выход 43 с третьими входами ячеек 15, 12 и 9 и четвертыми входамиячеек 6, 11 и 16, выход

44 с третьими входами ячеек 16, 13 и четвертыми входами ячеек 10, 15, а выход 20

45 — с третьим входом ячейки 17 и четвертым входом ячейки 14.

Вход 46 регистра горизонтального направления выборки 19 соединен с первыми выходами ячеек 2, 6, 10 и 14, вход 47 - 25 с первыми выходами ячеек 3, 7, 11 и 15, вход 48 — с первыми выходами ячеек 4, 8, 12 и 16, вход 49 — с первыми выходами ячеек 5, 9, 13 и 17. Вход 50 регистра вертикального направления выбор- 30 ки 24 соединен сэ вторыми выходами ячеек 2-5, вход 51 — co вторыми выходами ячеек 6-9, вход 52 — со вторыми выходами ячеек 10-12 и 13, вход 53 — со вторыми выходами ячеек 14-17. Вход 54 35 регистра диагонального растущего направления выборки 29 соединен с третьими выходами ячеек 2, 6, 10, 14-17, вход55с третьими выходами ячеек 3, 7, 11, 13, вход 56 — с третьими выходами ячеек 4, 4о

8 и 9 — вход 57 — с третьим выходом ячейки 5. Вход 58 регистра диагонального падающего направления выборки 34 соединен с четвертыми выходами ячеек 5, 4, 3 2-

6, 10 и 14, вход 59 — с четвертыми выходами ячеек 9, 8, 7, 11 и 15; вход

60 — с четвертыми выходами ячеек 13, 12 и 16, а вход 61 — с четвертым выходом ячейки 1 7.

Я}

Каждая ячейка 2-17 матрицы (например, ячейка 12, изображенная на фиг. 2) содержит запоминающий элемент 62, элементы

"И" 63-66. Выход запоминающего элемента 62 соединен с первыми входами элементов "И" 63-66, вторые входы которых подключены к выходам 41-43 блока 18 а выходы — к выходам 48, 52, 55 и 60 регистров 19, 24, 29 и 34, соответственно.

4

ЗУ работает следующим образом.

В матрице размером 4 х 4 ячейки возможны по 4 выборки слов в горизонтальном и вертикальном направлениях и по 7 выборок слов в диагональных направлениях.

В соответствии с этим адресный блок 18 имеет семь выходов 39-45, причем выходы 39-42 используются для выборок слов во всех направлениях, а выходы 4345 — для выборок слов в диагональных направлениях. Полный опрос всех ячеек матрицы осуществляется за семь тактов.

Допустим, что в запоминающих элементах верхней (ячейки 2-5) и нижней (ячейки 14-17) строк матрицы 1 записаны единицы, а в запоминающих элементах средних строк (ячейки 6-13) — нули.

Рассмотрим, например, третий такт работы устройства (на выходе 41 адресного блока 18 имеется разрешающий сигнал, на остальных выходах — запрещающие сигналы).

В соответствии со значением информации, записанной в запоминающих элементах матрицы, при появлении разрешающего сигнала на выходе 41 выходные сигналы вырабатываются только на выходе 58 ячейки

3, выходах 50, 56 ячейки 4 и выходе 53 ячейки 1 6. При этом в выходные регистры направлений выборки записываются следующие коды: в регистр 19 — кэд ОООО; в регистр 24 — код 1OOl; в регистр 29кэд OOlO; в регистр 34 — кэд 1000.

Направления выборки слов из 39 могут иметь любую конфигурацию, определяемую алгоритмом распознавания, например, углы, дуги, соединения, пересечения.

Формула изобретения

Запоминающее устройство с одновременной выборкой нескольких слов, содержащее матрицу изтп запоминающих элементов, адресный блок и и регистров направлений выборки, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит п тп элементов

И", первые входы которых подключены к выходам соответствующих запоминающих элементов, вторые — к выходам адресного блока, а выходы — к соответствующим входам регистров направлений выборки.

Источники информации, принятые во внимание при экспертизе:

1. Патент США Мо 3737866, кл.

340-172.5, 1973 r, 2. Патент США Ne 3643236, кл, 340173, 1972 г. (прототип).

542241

Г/У

2/ гг

46 г/

46 50 54

Г1

58 47 50 55! ! !

39 ЗУ

40 ЗУ 40 43

4/ 42

I 3

39

4/

42

43

44

/8

60

58

37

34 ЗЮ

38

Фцг./

ЗУ 42 39 40 40 4/

46 5/ 54 58 47 5/ 55

46 52 54 58 47 52 55

4/ 3Q 4/ 44 4/ 40 42 43

46 53 54 58 47 53 54

42 ЗУ 42 45 42 40 43 44

5S 4В 50 56 58 49 50 57 58!

4 5

39 4/ 44 40 3У 42 42 3У!

5У 48 5/ 56 5У 4У 5/ 56 59!

8 9

40 4/ 42 4/ 40 4г 43 40

5У 46 52 55 60 4У 52 55 бб!

/2 /3!

4/ 4/ 4З 42 4/ 42 44 4/ !!

59 48 53 54 60 49 53 54 6/!

/6 /7

42 4/ 44 43 42 42 45 42

54! 1

I!

i 29!

55!

3/ !!!!

56!

32!!!

57!! 33

542241

48 52

42

44

Составитель В. Рудаков

Редактор Л. Утехина Техред А. Демьянова Корректор Н. Ковалева

Заказ 5990/32 Тираж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород ул. Проектная, 4