Устройство для защиты памяти

Иллюстрации

Показать всеРеферат

ОП КСАН

Союз Советских

Социвлистииеских

Республик (61) Дополнительное к авт. свид-ву (22) ЗаявлЕно 03.10.75 (21) 2178646/24 с присоединением заявки № (23) Приоритет (43) Опубликовано 05.01.77. Бюллетень № 1 (45) Дата опубликования описания 28.02.77 (51) М. Кл.

G 11 С 29/00

Гасударственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК

681.327.6 (088.8) (72) Авторы изобретения

Ю. Г. Нестеренко и В. П. Супрун (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ

Изобретение относится к запоминающим устройствам.

Известны устройства для защиты памяти (1,2) .

В ряде известных устройств защищаемые зоны запоминающего устройства задаются с помощью 5 регистров граничных адресов или с помощью разбиения запоминающего устройства на отдельные участки с пометкой данных участков специальными признаками или ключами защиты памяти (1) .

Эти устройства не эффективны из-за относи- 10 тельно большого количества аппаратурных затрат: требуются два граничных регистра на каждую защищаемую область или наличие специальных элементов для пометки участков запоминающего устройства. И

Наиболее близко к предлагаемому устройство для защиты памяти, содержащее регистр адреса и регистр защиты, выходы которых подключены ко входам блока сравнения, выход которого соединен с однимизвходов основного элемента И,и индикатор (2l. о0

Однако в этом устройстве массив запоминающего устройства разделен на три фиксированные по функциональному назначению области: область с постоянной защитой информации от разрушения при записи, область с полупостоянной защитой, 25 защигцаемой от разру шения при определенном условии, и область, не защищаемую от разрушения информации при записи, что требует дополнительных затрат, объема запоминающего устройства дополнительного регистра лля за цищаемой области и дополнительного блока сравнения.

Цель изобретения — упрощение устройства для защиты памяти.

Предлагаемое устройство отличается тем, что оно содержит дополнительный элемент И, элемент

"Запрет" и элементы ИЛИ; входы первого элемента

ИЛИ подключены к выходу индикатора и шине доступа к памяти, а выход - к другому входу основного элемента И, выход дополнительного элемента И соединен с шиной прерывания, его входы— с выходами основного элемента И и второго элемента ИЛИ, входы которого подключены к шинам записи; один из входов элемента "Запрет соединен с выходом основного элемента И, другой — с шиной запрета, а выход — с выходной шиной устройтва.

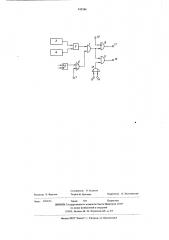

На чертеже изображена функциональная схема устройства.

Один вход элемента И 1 соединен с выходом блока сравнения 2, входы которого соединены с выходами регистра адреса 3 и регистра защиты 4.

542246

Между другим входом элемента И 1 и выходом индикатора 5 включен элемент ИЛИ 6. Один из его входов подключен к шине доступа к памяти 7.

Выход элемента И 1 подключен к сигнальному входу элемента "Запрет" 8 и к первому входу элемента И 9. Запрещающий вход элемента "Запрет" 8 подключен к шине запрета 10, à его выход— к выходной шине 11 устройства. Выход элемента

И 9 подключен к шине прерывания 12, а его второй вход — к выходу элемента ИЛИ 13, первый вход которого подключен к шине внутренней записи 14, а второй вход — к шине 15 записи от непосредственного доступа к запоминающему устройству.

Работает устройство следующим образом. Запоминающее устройство разбивается на две области — защищаемую и незащищаемую, причем величина защищаемой области определяется содержимым регистра 4. Блок сравнения 2 сравнивает содержимое регистра 4 с содержимым регистра адреса 3, и при обращении к защищаемой области запоминающего устройства на выходе блока сравнения 2 вырабатывается сигнал, который поступает на элемент И 1.

Для разных пользователей запоминающего устройтсва защита его производится по-разному.

Для внутреннего обращения к запоминающему устройству от процессора устройство срабатывает при наличии сигнала на выходе индикатора 5, состояние которого настраивается сигналами на его входе. При этом сигнал с индикатора, поступая через элемент ИЛИ б на элемент И 1, разрешает его включение, Сигнал с элемента И1 через элемент

"Запрет" 8 поступает на шину 11 для запрета выработки сигнала записи в запоминающее устройство.

Кроме того, сигнал с элемента И 1 поступает на первый вход элемента И 9, откуда на шину прерывания 12 приходит сигнал при наличии сигнала в запоминающее устройство, который, поступая с шины внутренней записи 14 через элемент ИЛИ 13 на второй вход элемента И 9, разрешает его включение. При отсутствии сигнала на выходе индикатора 5 устройство не вырабатывает сигнала запрета и сигнала требования прерывания при записи в область запоминающего устройства, определяемую регистром 4, так как элемент И 1 закрыт по одному из входов.

При попытке записи в защищаемую область запоминающего устройства при непосредственном доступе элемент И 1 открыт сигналом, поступающим с шины 7 через элемент ИЛИ 6, а элемент

И 9 открыт по второму входу сигналом, поступающим с шины 15 через элемент ИЛИ 13. При этом вырабатываются сигналы на шинах 11 и 12.

При прерывании сигнал запрета записи на ши® не 11 не вырабатывается, независимо от состояния выхода блока сравнения 2, так как на запрещающий вход элемента "Запрет" 8 поступает сигнал с шины запрета 10.

Таким образом, защищаемая область запоминающего устройства для различных пользователей представлена по-разному: для внутренних сигналов от процессора — условно защищаемая область, для сигналов непосредственного доступа — безусловно защищаемая область, а для сигналов процессора в режиме прерывания — безусловно незащищаемая область.

Формула изобретения

Устройство для защиты памяти, содержащее регистр адреса и регистр защиты, выходы которых подключены ко входам блока сравнения, выход которого соединен с одним из входов основного элемента И, и индикатор, от лича ющ ее ся тем, что, с целью упрощения устройства, оно содержит дополнительный элемент И, элемент "Запрет" и элементы ИЛИ, входы первого элемента ИЛИ подключены к выходу индикатора и шине доступа к памяти, а выход — к другому входу основного элемента И, выход дополнительного элемента И соединен с шиной прерывания, его входы — с выходами основного элемента И и второго элемента ИЛИ, входы которого подключены к шинам

40 записи, один из входов элемента Запрет соединен с выходом основного элемента И, другой — с шиной запрета, а выход — с выходной шиной устройства.

Источники информации, принятые во внимание при экспертизе:

4р 1. Папернов А. А., Логические основы цифровой вычислительной техники, "Сов. радио" М, 1972, стр. 525-527.

2. Патент Японии Х 49-30578, 97 (7) С01, 1974.

542246

Составитель В. Рудаков

Техред М. Ликович

Корректор Н. Золотовская

Редактор Б. Федотов

Заказ 5992/33

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4

Тираж 759 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5