Цифровой частотный дискриминатор

Иллюстрации

Показать всеРеферат

ОИИСAHИЕ, ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт, свид-ву (22) Заявлено11.12,75 (21) 2196999/21 с присоединением заявки № (23) Приоритет (43) Опубликовано05 01 77 Бюллетень № 1 (45) Дата опубликования описания 30.03.77 (51) М. Кл е

Н 03 3 13/00

Государственный комитет

Совета Министров СССР по делам изооретений и открытий (53) УДК 621,377. .33 (088.8) (72) Авторы изобретения

A. И. Овчаренко, А. К. Соловьев и В. М. Трохин (71) Заявитель

Украинский заочный политехнический институт (54) БИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР

Изобретение относится к импульсной технике.

Известен цифровой частотный дискриминатор, содержаший кварцевый генератор, шесть мультивибраторов, инверторы, два формирователя импульсов, логические элементы И, сдвигающий регистр, интегратор, детектор уровня, счетчики и логические схемы определения рассогласования (1) .

l0

Известен также цифровой частотный дискриминатор, содержащий формирователь, входы которого соединены с источниками тактовой и дискриминируемой частоты, а выход подключен к одним из входов логических )5 элементов 11, вторые входы которых соединены сэответствуюшими входами реверсивного счетчика, дешифратор, входы которого соединены с выходами реверсивного счетчика, вход установки которого соединен с источни-20 ком тактовой частоты, а выход соединен с одним из входов RS — триггера, резистор, выходы которого соединены со входами многоканального коммутатора, а вход записи соединен с выходом дешифратора.

Бель изобретения — упрошение дискриминатора, Поставленная цель достигается тем, что в предлагаемый дискриминатор, введен дополнительный дешифратор, и элемент задержки, причем входы дополнительнэгэ дешифратора соединены с соответствующими выходами реверсивного счетчика, а его выход соединен со вторым входом Я,$ — триггера, вход управления многоканальным коммутатором соединен через элемент задержкисвхэдом установки регистра и подключен к источнику тактового сигнала.

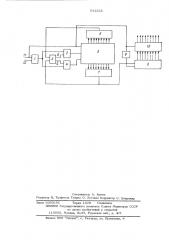

На чертеже изображена блок-схема предлагаемого дискриминатора, Дискриминатор содержит формирователь

1, КS -триггер 2, логические элементы 3 и 4, реверсивный счетчик 5, дешифратэры

6 и 7, элемент задержки 8, регистр 9 и многоканальный коммутатор 10. На входы

11 поданы сигналы тактовой частоты, а на вход 12 — сигнал дискриминируемой частоты.

Выходные сигналы снимаются с выходов многоканального коммутатора 10.

542328

Дискрим инат ор раб отает следую щи м образом, При низком уровне тактовой частоты блокируется прохождение импульсов дискриминируемой частоты через формирователь 1. Од- 5 нэвременно R -триггер 2 устанавливается в такое состояние, при котором на выходе

6 пэявляется высокий уровень, а на выходе Q — низкий уровень, т.е. подготовлена цепь прохэждения импульсов дискримини- 10 руемой частоты на суммирующий вход реверсивнoro счетчика 5 через элемент 3. Про,хождение импульсов дискриминируемэй часToTbl на вь|читаюший вхэд реверсивногэ счетчика 5 через элемент 4 блокируется. Кроме i того, при низком уровне тактовой частоты устанавливается реверсивный счетчик 5, разрешается считывание информации коммута— тором 10 с регистра 9 и через определенное время устанавливается регистр. цискри- >О минатэр готов к работе.

, и пояьлении высокого уровня тактовэй

i.à",ñeòoò,; импульсы дискриминируемой частоты прэхэдят на суммируюший вход реверсивнэгэ счетчика 5, и, когда в счетчике записывается максимальное число (соответствующее числу его разрядов), на выходе дешифрат эра 6 п оявляется низкий ур овень. При этом переключается 8.$ -триггер 2, и импуль. сы дискриминируемэй частоты проходят на вычитающий вход реверсивного счетчика 5, Как только число импульсов, поступивших на вычитающий вход, сравнивается с числом импульсов, поступивши.х на суммируюший вход (т.е. в счетчике 5 записывается число

О), на выходе дешифратэра 7 появляется низкий уровень, переключающий ЗЬ- триггер

2, и импульсы дискриминируемой частоты проходят на суммирующий вход, Такая поочередная работа реверсивного счетчика 5 на

40 суммирэвание и вычитание продолжается в течение всегэ измерения. Выходные импульсы дешийэатора 7, появляющиеся через каждые 2 2 импульсов дискриминируемой часToTb1 (где и — количество разрядов реверсивного счетчика 5 ), подаются íà вход запи— си регистра 9. По экончании времени измере ния, т.е. при низком уровне тактовой частоты, записанное в регистре 9 числэ считывается и возбуждается одним из каналов коммутатора 10. Через эпределеннэе время устанавливается регистр 9, и работа цифрового частотного дискриминатора повторяется.

За счет попеременного суммирования и вычитания в реверсивном счетчике уменьшается количество его разрядов, что ведет к упрощению дискриминатора.

Формула из обретения

Бифр ов ой част отный дискрим инат ор с эдержаший формирователь, входы которого соединены с источниками тактовой и дискриминируемой частоты, а выход подключен к одним из BKogoB логических элементов И, втэрые вхэды которых соединены с сэответствуюшими входами реверсивногэ счетчика, дешифратор, входы которого соединены с BbI.ходами реверсивнэго счетчика, вход устанэвки которого соединен с источником тактовой частоты, а выход соединен с одним из входов g$ -триггера, резистор, выходы котэрэго соединены со входами мнэгоканальнэгэ коммутатора, а вход записи соединен с выходом дешифратора, э т л и ч а ю щ и йс я тем, что, с целью его упрощения в него введен дополнительный дешифратэр и элемент задержки, причем входы дolIолните IbHэro дешифратэра соединены с соответствующими выхэдами реверсивного счетчика, à его выход соединен со вторым входом 8 S -òðèrrepa, вход управления многоканальным кэммутаторэм соединен через элемент задержки с входом установки регистра и подключен к источнику тактового сигнала.

Источники информации, принятые во внимание при экспертизе:

1. Патент США % 3418586, кл. 329-104, 24,12.68.

542328

Составитель А. Артюх

Редактор В, Трофимов Техред О. Луговая Корректор C. Болдижар

Заказ 6000/36 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4