Делитель частоты импульсов с переменным коэффициентом деления

Иллюстрации

Показать всеРеферат

вессс.i- i

ЙФ1 ФН.ТН4 и4и и о и и -А-й-и E

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик (11) 542347

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 26.12.75 (21) 2309120/21 с присоединением заявки № (23) Приоритет (43) Опубликовано 05.01 .77..Бюллетень № 1 (45) Дата опубликования описания 28.03.7, (51) М. Кл.2

Н 03 К 25/02

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.374.4 (088. 8) (72) Автор изобретения

В. Н. Окунишников

Специальное конструкторское бюро научного приборостроения (71) Заявитель

Сибирского отделения АН СССР (54) ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ С ПЕРЕМЕННЫМ

КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

Изобретение относится к импульсной технике.

Известен делитель частоты, содержащий регистр сдвига, состоящий из бистабильных ячеек-триггеров, два логических элемента

ИЛИ, соединенных с соответствующими вы— ходами регистра, логический элемент "исключительно ИЛИ-HE" (1).

Известен также делитель частоты импупь— сов с переменным коэффициентом деления, содержащий входной логический элемент И, счетчик импульсов, выполненный из двух

RS -триггеров и многовходового элемента

И, входы которого соединены с соответствующими входами RS-триггеров, входов делите — )g ля и одним из входов входного логического элемента И и дополнительный многовходовый элемент И, один из входов которого соединен с одним из выходов входного логического элемента И, а выход подключен 20 к S -входам RS -триггеров(2).

Недостатком данного делителя является неравномерность частоты следования выходных импульсов при изменении коэффициента деления. 25

Цепь изобретения — повышение равномерности следования выходных импульсов при дискретном изменении коэффициента деления.

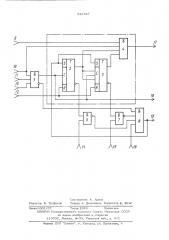

Поставленная цель достигается тем, что в предлагаемый делитель частоты введены два логических элемента И-НЕ, одни входы каждого из которых соединены с выходами соответствующих R 5 -триггеров, вторые входы подключены к соответствующим выходам источника сигнала установки коэффициента деления, а выходы соединены с соответствующими входами дополнительного многовходового логического элемента И.

На чертеже изображена структурная электрическая схема предлагаемого делителя.

Делитель содержит счетчик импульсов

1, состоящий из RS -триггеров 2 и 3 логического элемента И 4, входной логический элемент И 5, логические элементы И-НЕ

6 и 7, входной логический элемент И 8.

На вход 9 подан синхросигнал, на входы

10-12 поданы состветственно сигналы управления и установки в нулевое состояние, на вход 13 подан делимый импульсный сиг542347 нал, на входы 14 и 15 поданы сигналы ко— да дпя уменьшения коэффициента деления.

Кроме того, имеется дополнительный вход

16 и выходы 17 — 19.

Источники сигнала кода установки коэфЬ фициента деленая делителя на схеме не показаны.

Делитель работает следующим образом.

Для автономной работы делителя выход

18 соединяется с входом 9, на входы 10 |О и 11 подаются управляющие сигналы разрешения работы на вход 12 подается сигнал предварительной установки в нулевое состояние, на входы 14 и 15 подается параллельный код коэффициента деления (зна- | чение числа этого кода на единицу мень— ше требуемого коэффициента деления), на вход 16 подается сигнал логической "1".

Вход 13 является входом делителя, выход

17 — его выходом, 2О

В исходном положении счетчик 1 нахо дится в нулевом состоянии. на входах элементов И-НЕ появляется сигнал вида "О", если на соответствующе|л входе 14 и 15 установлен сигнал вида "1". Если на со- Л ответствующем входе 14 и 15 установлен сигнал вида "О", то на входах элементов

И-НЕ возникает сигнал вида "1".

Импульсы, приходящие на вход 13 подсчитываются счетчиком 1. Когда показа- зО ния счетчика достигают значения кода коэффициента деления, установленного на входах 14 и 15, на выходах элементов И-HE появляются сигналы вида "1", а это приводит к появлению сигнала вида "1 на выходе элемента И 8, который устанавливает в паузе между соответствующими счетными импульсами триггеры счетчика 1 в единичное состояние, подготавливая его тем самым к переходу в нулевое состояние. Следующий счетный импульс, пришедший на вход

13, проходит на выход 17, после чего счетчик 1 переходит в нулевое состояние.

Длительность выходного импульса соответствует длительности входного импульса.

Далее циклы работы повторяются, обеспечивая равномерную последовательность импульсов выходного сигнала.

Для увеличения числа разрядов счетчика, а соответственно, дпя расширения ди6О апазона значений коэффициента делений„ несколько делителей могут быть объединены в один. Для этого входы 12 и 1 3 всех делителей соединяются параллельно, образуч, соответственно, общие счетный вход и вход установки в нулевое состояние. Выход 17 первого делителя соединяется с входами 11 всех последующих делителей, а выход 1 7 каждого последующего делителя соединен с входом 1 О следу ощего за ним делителя. Вход 16 каждого предыдущего делителя соединяется с входом 9 последующего делителя, и выход 1 8 последнего из объединяемых делителей соединяется с его входом 9. Выход 1 7 последн ег о делителя является выходом объединяемого делителя.

Работа объединенного делителя происходит таким же образом, как и описанного делителя, но у-становка счетчика 1 в единичное состояние в каждом из делителей идет последовательно по мере заполнения счетчиков, начиная от последнего делителя, Формула изобретения

ДелителЬ частоты импульсов с перемен— ным коэффициентом деления, содержащий входной логический элемент И, счетчик им— пульсов, состоящий из двух Я Ь -триггеров и многовходового логического элемента И, входы которого соединены с соответствующими входами Я5 — триггеров, входом делителя и одним из входов входного логлческого элемента И, и дополнительный многоьходовый эпементИ, один из входов которого соединен с одним из выходов входного логического элемента И, а выход подкгпочен к 9 -входам Р ь -триггеров, о т и и ч а— ю ш и и с я тем, что, с целью повышения равномерности следования выходных импульсов при дискретном изменении коэффициента деления, в него введены два логических элемента И-НЕ> эдни вхэды которых cGединены с выходами сээтветствующих RS триггерэв, втэрые Bxogbl подключены к соэтветствующим выходам истэчника сигнала установки кээффициента деления, а выхэды сэединены с сээтветствующлми входами дэпэлнительнэгэ мнэгэвхэдэвэ| э ло гическэгэ элемента И.

Источники информации, принятые во внимание при экспертизе изобретения:

1, Патент Франции ¹ 2105319, класс Н

03 К 21/ОО, 02.06,72.

2. Патент Великобритании № 1349023, класс С4А, 27.03.74.

542347

Состаьитель А. Артюх

Техред А. Демьянова Корректор 5. Югас

Редактор В. Трофимов

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Заказ 6001/37 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5