Накопительный сумматор параллельного действия

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (i i) 542994

К АВТОРСКОААУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 07,03.74 (21) 2006161/24 с присоединением заявки № (23) Приоритет

Опубликовано 15.01.77. Бюллетень № 2

Дата опубликования описания 07.02.77 (51) М. Кл.з 6 06F 7/385

Государственный комитет

Совета Мнннстров СССР ло делам изобретений н открытнй (53) УДК 681.325(088.8) (72) Авторы изобретения

В. П. Боюн, Н. С. Гаврилюк и Л. Г. Коз

8 fl y g (71) Заявитель

Ордена Ленина институт кибернетики

АН Украинской ССР (54) НАКОПИТЕЛЪНЫЙ СУММАТОР ПАРАЛЛЕЛЪНОГО

ДЕЙСТВИЯ

Изобретение относится к вычислительной технике и может быть использовано при построении процессоров цифровых вычислительных машин.

Известен сумматор, содержащий в каждом 5 разряде, триггер, вход которого соединен с выходом первого элемента ИЛИ, подключенного первым входом к выходу первого элемента И, а вторым входом — к выходу второго элемента И, первый вход которого соединен с 1О первым входом третьего элемента И, ко второму входу которого подключен прямой выход

TpHrrepa, инверсный выход которого соединен с первым входом четвертого элемента И, выход которого соединен с первым входом вто- 15 рого элемента ИЛИ, подключенного вторым входом к выходу третьего элемента И, а выходом — к первому входу третьего элемента И соседнего старшего разряда, входная шина соединена со вторыми входами первого и чет- 20 вертого элементов И, а управляющие входы устройства соединены с вторыми входами первого и второго элементов И (1, 2). Однако известный сумматор имеет низкое быстродействие, так как суммирование осуществляется в 25 два такта, в первом из которых происходит занесение слагаемого в триггеры и формирование сигналов переноса, а во втором такте производится повторное изменение состояния триггеров в соответствии со сформированны- 30 ми в первом такте сигналами переноса. Изве. стно также устройство, реализующее идею ускорения распространения сигнала переноса за счет использования обходных цепей и содержащее два регистра слагаемых, регистр результата, комбинационную часть для выработки сигналов суммы и переноса, а также блоки для ускорения прохождения сигналов через группу разрядов переноса (3). Этот сумматор имеет большой объем оборудования и малое быстродействие, так как время сложения в режиме многократного суммирования равно удвоенному времени переброса триггера и времени задержки сигнала в комбинационной части. Наиболее близким к изобретению техническим решением является накопительный сумматор параллельного действия, содержащий в каждом разряде первый триггер, выход которого соединен с первым входом блока анализа, первый выход которого соединен с нулевым входом первого триггера, второй триггер, выход которого соединен со вторым входом блока анализа, третий вход блока анализа каждого разряда соединен со вторым выходом блока анализа предыдущего разряда (4). Он характеризуется также низким быстродействием, так как затрачивается большое время иа распространение сигнала переноса в последовательной цепочке блоков анализа.

542994

55

65

Целью изобретения является повышение быстродействия. B описываемом сумматоре это достигается тем, что в него введены элементы

И, инверторы и элементы запрета, причем в каждом разряде входы первого элемента И соединены с двумя входами элемента запрета, которые соединены соответственно с первым и вторым входами блока анализа, выход первого элемента И соединен с первыми входами второго н третьего элементов И и через инвертор — с первым входом четвертого элемента И, второй вход которого соединен с управляющей шиной и со вторым входом третьего элемента И, выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с выходом элемента запрета, а выход подключен к единичному входу триггера, выход четвертого элемента И соединен с четвертым входом блока анализа, третий вход которого соединен с третьим входом элемента запрета и вторым входом второго элемента И, выход которого соединен со вторым выходом блока анализа, входы первых элементов И соседних разрядов через шестые элементы И подключены к первому входу седьмого элемента И, второй вход которого подключен ко второму входу второго элемента

И младшего из этих разрядов, а выход — к выходной шине, входы шестых элементов И соседних разрядов подключены через восьмой элемент И к первому входу девятого элемента И, второй вход которого подключен ко второму входу второго элемента И младшего из этих разрядов, а выход — к выходной шине.

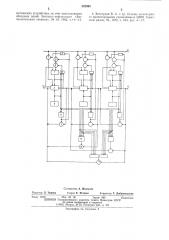

На чертеже приведена схема описываемого сумматора.

Он содержит в каждом разряде первые триггеры 1, вторые триггеры 2, блоки анализа

3, первые, вторые, третьи, четвертые и пятые элементы И 4, 5, 6, 7 и 8, инверторы 9, элементы запрета 10; управляющую шину 11, входную шину 12 и выходную шину 13, шестые, седьмые, восьмые и девятый элементы И

14, 15, 16 и 17.

Первое слагаемое находится в первых триггерах 1, второе — во вторых триггерах 2, перенос формируется блоками анализа 3. Элементы И 4 вырабатывают сигнал на выходе, если состояния обоих триггеров 1 и 2 данного разряда не «нулевые». Если в аналогичном состоянии находятся триггеры 1 и 2 двух или трех соседних разрядов, то вырабатывается управляющий сигнал на выходах соответствующих элементов И 4. В зависимости от кодов чисел, содержащихся в триггерах 1 и 2, элементы И 4 разрешают сигналу переноса со входной шины 12 проходить на выходную шину 13 по наикратчайшему пути, Если в какомлибо разряде триггеры 1 и 2 находятся в состоянии «1» и на входе блока анализа 3 этого разряда есть сигнал переноса с предыдущего разряда, то сигнал с выхода элемента запрета

10 закрывает пятый элемент И 8, запрещая сброс триггера 1 в «О». Если оба триггера 1 и

2 в каком-либо разряде находятся в состоя5

45 нии «О», то через инвертор 9 открывается четвертый элемент И 7, и импульс сложения поступает с управляющей шины 11 на вход соответствующего блока анализа 3.

Описываемый накопительный сумматор параллельного действия имеет большее быстродействие, по сравнению с известными накопительными сумматорами, в которых суммирование осуществляется за два такта, в то время, как в описываемом сумматоре — за один такт.

Формула изобретения

Накопительный сумматор параллельного действия, содержащий в каждом разряде первый триггер, выход которого соединен с первым входом блока анализа, первый выход которого соединен с нулевым входом первого триггера, второй триггер, выход которого соединен со вторым входом блока анализа, третрий вход блока анализа каждого разряда соединен со вторым выходом блока анализа предыдущего разряда, отличающийся тем, что, с целью повышения быстродействия, он содержит элементы И, инверторы и элементы запрета, причем в каждом разряде входы первого элемента И соединены с двумя входами элемента запрета, которые соединены соответственно с первым и вторым входами блока анализа, выход первого элемента И соединен с первыми входами второго и третьего элементов И и через инвертор — с первым входом четвертого элемента И, второй вход которого соединен с управляющей шиной и со вторым входом третьего элемента И, выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с выходом элемента запрета, а выход подключен к единичному входу триггера, выход четвертого элемента И соединен с четвертым входом блока анализа, третий вход которого соединен с третьим входом элемента запрета и вторым входом второго элемента И, выход которого соединен со вторым выходом блока анализа, входы первых элементов И соседних разрядов через шестые элементы И подключены к первому входу седьмого элемента И, второй вход которого подключен ко второму входу второго элемента И младшего из этих разрядов, а выход— к выходной шине, входы шестых элементов И соседних разрядов подключены через восьмой элемент И к первому входу девятого элемента И, второй вход которого подключен ко второму входу второго элемента И младшего из этих разрядов, а выход — к выходной шине.

Источники информации, принятые во внимание при экспертизе:

1, Папернов А. А. Логические основы цифровой вычислительной техники. М., Советское радио, 1972, с. 159, рис. 14.

2. Карцев М. А. Арифметика цифровых машин, M., Наука, 1969, с. 249, рис. 2 — 45.

3. Лехман М. н Вурла Н. Ускорение распространения сигнала переноса в двоичных ариф542994

Составитель А. Шкатулла

Техред Е. Петрова

Редактор Л. Тюрина

Корректор Т. Добровольская аказ 103/5 Изд. № 101 Тираж 899 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 метических устройствах за счет использования обходных цепей. Экспресс-информация «Вычислительная техника», № 19, 1962, с. ° 1 — 13.

4. Хетагуров Я. А. н др. Основы ннженсрного проектирования управляющих ЦВМ. Советское радио, М., 1972, с. 104, рнс. 4 — 17.