Ячейка памяти для регистра сдвига

Иллюстрации

Показать всеРеферат

ОПИСА-Н

ИЗОБРЕТЕН ИЯ

И Е

1111 5430I 3

Со1оз Советских

Социалистических

Реслублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 28.12.73 (21) 1981916/24 с присоединением заявки № (23) Приоритет

Опубликовано 15.01.77. Бюллетень ¹ 2

Дата опубликования описания 18.02.77 (51) М. Кл 2 G 11С 19/28

Государственный комитет

Совета Министров СССР

iI0 делам изобретений и открытий (53) УДК 681.327.66 (088.8) (72) Авторы изобретения

В. Ф. Маркин и В. В. Прушинский (71) Заявитель

Московский ордена Трудового Красного Знамени инженерно-физический институт (54) ЯЧЕЙКА ПАМЯТИ ДЛЯ РЕГИСТРА СДВИГА

Изобретение относится к вычислительной технике и предназначено для построения линий задержки и устройств памяти цифровых вычислительных устройств.

Известна ячейка памяти регистра сдвига, включающая два двухэмиттерных транзистора, причем коллектор первого подключен к базе второго и через первый резистор — к шине питания, коллектор второго — к базе первсго и через второй резистор — к шине питания. Первые эмиттеры двухэмиттерных транзисторов подключены ко входам ячейки пам1пи, а вторые объединены с шиной тактовых импульсов. Коллекторы двух эмиттерных тра1 зисторов соед1шепы с выходами ячейки

11ам1п и. Эта известная ячейка памяти имеет невысокое быстродействие, так как переключается частью тока, текущего через один из коллскторных резисторов. Известна также ячейка памяти для регистра сдвига, содержащая транзисторы, база первого из которых подключена к коллектору и базе первого и второго триггерных транзисторов и через первый резистор — к катоду диода, анод которого соединен с шиной тактовых импульсов.

База второго транзистора соединена с коллектором и базой второго и первого многоэмиттсрных транзисторов it через второй резистор — с катодом диода и шиной питания, коллекторы первого и второго транзисторов подключены к выходам ячейки памяти, а базы первого и второго транзисторов соединены со входами ячейки памяти. Эмиттеры всех транзисторов объединены с шиной пулевого потенциала. Однако все известные схемы характеризуются невозможностью осуществления î.tcрации обратного сдвига, т. е. реверсивного режима работы.

Целью изобретения является расширение

1О области применения ячейки памяти в виде получения дополнительной функции обратного сдвига без существенного увеличения площаjItt, занпмаек1ой ячейкой IIBMIITH H2 кристал.II" интегральной схемы. B описываемой ячейке

15 это достигается тем, что в нее введены дополнительные транзисторы, шины прямого 11 обратного сдвига, база первого допол1штельного транзистора подключена к базе первого транзистора и к одному пз дополнительных

«О входов ячейки памяти, один пз дополнптель11ых выходов ко t opots ttpttcoeд11пеп к коллектору первого дополнительного транзистора, база второго дополнительного транзистора подключена к базе второго транзистора и к

25 другому дополнительному входу ячейки памяти, другой дополнптсльньш выход которой подсоедпнсн к коллектору второго дополшпельного транзистора, эмиттеры дополнительных транзисторов и первые эмпттеры многоэмит30 тсрных транзисторов соединены с шиной об543013 р;пного сдвига, <1 эм1птсры транзисторов ll вторыс эыптсры х!Во!.Оэ1!!ггтсрц!.!х траизистоРОВ ПОДКЛ10 !СНЫ ILIIIIIC ВРЯД!0! 0 СДВИГ; !.

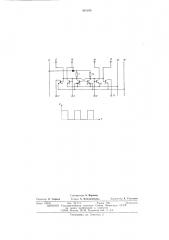

11а чертеже приведена ириицIIIIIIHльиа»

JлсK1Ри !сск!I II схcь!11 0111lcывclсыОЙ и Icйк!I пilм яти.

Она содерж!п первый транзистор 1, база которого подключена к «оллектору первого многоэмпттерного транзистора 2, к базе второго многоэмиттерного транзистора 3, к базе перВого дополш!тельного транзистора 4, и первому Входу 5, к первому дополнительному входу 6 и через первый резистор 7 — и катоду диода 8, анод которого соединен с шиной тактовых импульсов 9. База второго транзистора

10 соед!!непа с коллектором транзистора 3, с базой транзистора 2, с базой второго дополнительного транзистора 11, со вторым входом 12, со вторым дополнительным входом 13 и через второй резистор 14 — с катодом диода

8. Коллектор транзистора 1 объединен с первым выходом 15, а коллектор транзистора

10 — со вторым выходом 16. Коллектор транзистора 4 связан с первым дополнительным выходом 17, а коллектор транзистора 11 — со вторым дополнительным выходом 18. Дополнительные эмпттеры транзисторов 2 и 3 и эмиттеры транзисторов 4 и 1! соединены с шиной обратного сдвига 19, а эмиттеры транзисторов 1, 2, 3 и 10 — с шиной прямого сдвига 20. При работе ячейки памяти в составе регистра сдвига выходы 15 и 16 данной ячейки объединяются соответственно со входами 5 и

12 последующей ячейки, а выходы 17 и 18 данной ячейки — со входами 6 и 13 предыдущей ячейки.

Пусть на шине 20 действует низкий, а на шине 19 высокий уровни потенциала. Высокий уровень потенциала на шине 19 обеспечивает закрытое состояние транзисторов 4 и 11. Транзисторы 1, 2, 3 и 10 данной ячейки закрыты, а на шине 9 отсутствует тактовый импульс.

На базе транзистора 10 действует низкий уровень потенциала, обусловленный насыщенным состоянием транзистора 10 предыдущей ячейки. При этом данная ячейка работает в режиме приема информации.

С приходом тактового импульса транзисторы 1 и 3 данной ячейки открыва1отся током через резистор 7, а транзистор 2 остается закрытым. Такое направление переходного процс(са В !! Iсй! с ОосспсчпВ11стся зарядом, п11-!.оплсипым в базе транзистора 10 предыдуи1сй ячейки, ко!Орый иод,!Сржпвает потенциал базы транзистора 2 да!!Вой ячейки иа низком

> уровис Во Время Включения транзистора 3.

51 !с!!к работает В рс и!!1!с храпения и передачи !шформац!ш.

Из приведеш!Ой работы видно, что в ячейке памяти осуществляется прямой сдвиг инфорх!ации, если на шипе 20 действует низкий, а па шине 19 высокий уровень потенциала.

Обратный сдвиг информации в ячейку осуществляется аналогично при подаче на шину

19 низкого, а на и!ш1у 20 высокого уровня по!

5 . енциала.

Формула изобретения 1чсйка памяти для регистра сдвига, содержащая транзисторы, база первого из которых

23 подключена к коллектору и базе первого и второго миогоэмиттерных транзисторов и через первый резистор — к катоду диода, анод которого соединен с шиной тактовых импульсов, база второго транзистора соединена с

2> коллектором и базой второго и первого многоэмпттер ых транзисторов и через второй резистор — с катодом д!юда и шиной питания, коллекторы первого и второго транзисторов подключены к выходам ячейки памяти, базы

ЗП первого и второго транзисторов соединены со входами ячейки памяти, отличающаяся тем, что, с целью расширения области применения ячейки па!!яти, в иее введены дополнительные транзисторы, шины прямого и обрат35 ного сдвш.а, база первого дополнительного транзистора подключена к базе первого транзистора и к одному из дополнительных входов ячейки памяти, один из дополнительных выходов которой присоединен к коллектору

4О первого дополнительного транзистора, база второго дополнительного транзистора подключена к базе второго транзистора и к другому дополнительному входу ячейки памяти, другой дополнительный выход которой подсоеди45 нен к коллектору второго дополнительного транзистора, эмиттеры дополнительных транзисторов и первые эмиттеры многоэмиттерных транзисторов соединены с шиной обратного сдвига, эмиттеры транзисторов и вторые эмит50 теры многоэмиттср ы транзисторов подключены к шине прямого сдвига.

Составитель А. Воронин

Техред А. Камышникова

Редактор Л. Тюрина

1(орректор А, Галахова

Типография, пр. Сапунова, 2

Заказ 109121 Изд. № 111 Тираж 769 Г!одписиос

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изооретеиий и открытий

113035, Москва, 5К-35, Раушская нао., и. 4 5