Декодирующее устройство для циклс ческих мажоритарных двоичных кодов с избыточностью при многократном повторении сообщений

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВЫДЕТЕЛЬСТВУ (ii) 543174

Союз Советских

Социалистических

Республик (61) Дополнительнос к авт. свпд-ву 261460 (22) Заявлено 02.04.74 (21) 2012088/09 (51) М. Кл. Н 041 I, 10

H ОЗК 5/01

Н ОЗК 13/00 с присоединением заявки №

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий (23) Приоритет

Опубликовано 15.01.77. Бюллетень ¹ 2

Дата опубликования описания 14.02.77 (53) УДК 621.394.142:621. .376.56 (088.8) (72) Автор изобретения

В. И. Ключко (71) Заявитель (54) ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО

ДЛЯ ЦИКЛИЧЕСКИХ МАЖОРИТАРНЫХ

ДВОИЧНЫХ КОДОВ С ИЗБЫТОЧНОСТЬЮ

ПРИ МНОГОКРАТНОМ ПОВТОРЕНИИ СООБЩЕНИЙ

Изобретение относится к технике связи и может использоваться в аппаратуре повышения достоверности передачи цифровой информации.

По основному авт. св. № 261460 известно устройство, содержащее регистр сдвига с подключенными к его параллельным выходам сумматорами по модулю два, выходы которых через распределители подключены последовательно к счетчикам мажоритарных проверок с числом, равным числу информационных элементов, проверки выполнены по схеме с одним порогом срабатывания для всех повторений (1).

С целью повышения быстродействия устройства в него введены блок сравнения и блок памяти, при этом выходы счетчиков мажоритарных проверок, соответствующих различным порогам срабатывания, подключены к соответствующим входам блока сравнения непосредственно и через блок памяти.

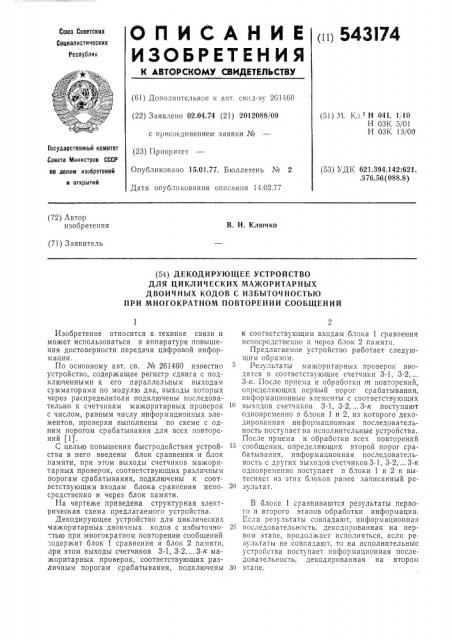

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Декодирующее устройство для циклических мажоритарных двоичных кодов с избыточно"тью при многократном повторении сообщений

"одержит блок 1 сравнения и блок 2 памяти, при этом выходы счетчиков 3-1, 3-2, ... 3-к мажоритарных проверок, соответствующих различным порогам срабатывания, подключены к соответствующим входам блока 1 сравнения непосредственно и через блок 2 памяти.

Предлагаемое устройство работает следующим образом.

Результаты мажоритарных проверок вводятся в соответствующие счетчики 3-1, 3-2, ...

3-к. После приема и обработки ттт повторений, определяющих первый порог срабатывания, информационные элементы с соответствующих

10 выходов счетчиков 3-1, 3-2, ... 3-к поступают одновременно в блоки 1 и 2, из которого декодированная информационная последовательность поступает на исполнительные устройства.

После приема и обработки всех повторений сообщения, определяющих второй порог срабатывания, информационная последовательность с других выходов счетчиков 3-1, 3-2, ... 3-к одновременно поступает в блоки 1 и 2 и вытесняет из этих блоков ранее записанный ре20 зультат.

В блоке 1 сравниваются результаты первого и второго этапов обработки информации.

Если результаты совпадают, информационная

25 последовательность, декодпрованная на первом этапе, продолжает исполняться, если результаты не совпадают, то на исполнительныс устройства поступает информационная последовательность, декодированная на втором

30 этапе.

543174

Формула изобретения

Составитель О. Тихонов

Техред А. Камышникова Корректор И, Позняковскаа

Редактор Т. Янова

Заказ 105/13 Изд. Яв 112 Тираж 869 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

1!3035, Москва, Раушская иаб., д. 4/5

Типография, пр. Сапунова, 2

Декодирующее устройство для циклических маиоритарных двоичных кодов с избыточностью при многократном повторении сообщений по авт. св. Хо 261460, отличающееся тем, что, с целью повышения быстродействия, введены блок сравнения и блок памяти, при этом выходы счетчиков мажоритарных проверок соответствующих различным порогам срабатывания, подключены к соответствующим входам блока сравнения непосредственно и через блок памяти.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство Мв 261460, М. Кл.2 Н ОЗК 5/01, 1968 г. (прототип).