Устройство синхронизации по циклам в дискретном канале связи

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (и) 543)8!

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 27.06.75 (21) 2149569/09 с присоединением заявки № (32) Приоритет

Опубликовано 15.01.77. Бюллетень № 2

Дата опубликования описания 14.02.77 (51) М Кл Н 04L ?/02

Государственный комитет

Совета Министров СССР (53) УДК 621.394.662.2 (088.8) ло делам изобретений и открытий (72) Авторы изобретения (71) Заявитель

В. С. Кузькин и М. П. Наумчик

Московский ордена Трудового Красного Знамени электротехнический институт связи (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ ПО ЦИКЛАМ

В ДИСКРЕТНОМ КАНАЛЕ СВЯЗИ

К= Ю, где У вЂ” число участков разбиения периода цикловой синхронизации. Формиро30 ватели 8 стробов образуют для соотвествуюИзобретение относится к технике передачи дискретных сообщений, Известно устройство синхронизации по циклам в дискретном канале связи, содержащее делитель частоты, выходы ячеек которого подключены к входам формирователя синхросигналов, и дешифратор маркерных групп, выход которого подключен через элементы И к соответствующим накопителям (11.

Однако известное устройство имеет большое время вхождения в синхронизм.

С целью сокращения времени вхождения в синхронизм в предлагаемом устройстве синхронизации по циклам в дискретном канале связи выходы каждой ячейки делителя подключены к вторым входам соответствующих элементов И через введенные формирователи стробов, причем выходы накопителей подключены к дополнительным входам формирователя синхросигналов через введенные блоки выделения максимума.

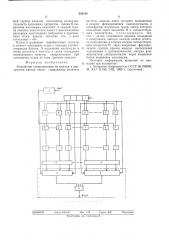

На чертеже приведена функциональная схема устройства.

Устройство синхронизации по циклам в дискретном канале связи содержит делитель 1 частоты, выходы ячеек которого подключены к входам формирователя 2 синхросигналов, состоящего из блоков 3 сравнения и схемы 4 совпадения, дешифратор 5 маркерных групп, выход которого подключен через элементы И 6 к соответствующим накопителям 7, причем выходы каждой ячейки делителя 1 частоты подключены к вторым входам соответствующих элементов И 6 через введенные формирователи 8 стробов, а выходы накопителей 7 подключены к дополнительным входам формирователя 2 синхросигналов через блоки 9 выделения максимума.

Устройство работает следующим образом.

10 Дешифратор 5 маркерных групп опознает маркерную группу в информационном разряде.

Делитель 1 частоты, формирователи 8 стробов, элементы И 6, накопители 7 и блоки 9

15 выделения максимума образуют анализирующий узел, который опознает после накопления в течение заданного числа циклов, связанного с требуемой помехоустойчивостью, номера каналов по каждой из т групп, соответст23 вующие позиции цикла, в которой с наибольшей вероятностью присутствуют импульсы с дешифратора маркерных групп 5.

Каждая ячейка делителя частоты 1, содержащего и ячеек, делит поступающую на ее

25 вход последовательность импульсов на

543!Я!

1!!

" !! ! ! ! !

Изд, 112

Заказ 449/10

ЦНИИПИ

Тнраяс 882

Подписное

Типография, пр. Сапунова, 2 щей группы каналов накопления последовательность временных дискретов. Блоки 9 выделения максимума выделяют в каждой группе каналов накопления канал с максимальным значением накопленных импульсов и присваивают этому каналу значение «1», а всем остальным — «0».

Блоки 3 сравнения вырабатывают сигналы в момент совпадения кодов с выходов соответствующих блоков 9 выделения максимума и ячеек делителя частоты, а схема совпадения вырабатывает импульс синхронизации при совпадении кодов по всем группам каналов.

Формула изобретения

Устройство синхронизации по циклам и дискретном канале связи, содержащее делитель частоты, выходы ячеек которого подключены к входам формирователя синхросигналов, и дешифратор маркерных групп, выход которого подключен через элементы И к соответствующим накопителям, отл и ч а ю щееся тем, что, с целью сокращения времени вхождения в синхронизм, выходы каждой ячейки делителя подключены к вторым входам соответствующих элементов И через введенные формиро-!

О ватели стробов, причем выходы накопителей подключены к дополнительным входам формирователя синхросигналов через введенные блоки выделения максимума, Источник информации, принятый во вни15 мание при экспертизе:

1. Авторское свидетельство СССР № 336826, М. Кл. Н 041 7/02, 1969 г, (прототип).