Распределитель адреса линий для автоматических систем коммутации

Иллюстрации

Показать всеРеферат

О П И С А Н И Е ((() 543198

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 02.01.74 (21) 1984325/09 с присоединением заявки Ке (23) Приоритет

Опубликовано 15.01.77. Бюллетень )ч" 2

Дата опубликования описания 02.02.77 (51) М. Кл.- Н 04М 3/18

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.395.34 (088.8) (72) Авторы изобретения

В. 3. Равич и Ю. Л. Закгейм (71) Заявитель Ленинградское отделение Центрального научно-исследовательского института связи (54) РАСПРЕДЕЛИТЕЛЬ АДРЕСА ЛИНИЙ

ДЛЯ АВТОМАТИЧЕСКИХ СИСТЕМ КОММУТАЦИИ

Изобретение относится к технике связи и может использоваться в автоматических системах коммутации.

Известны распределители адреса линий для автоматических систем коммутации, содержашие р аспределители, выполненные по схеме счетчика, и дешифраторы, построенные на схемах совпадения, причем число входов каждой схемы совпадения соответствует числу разрядов счетчика.

Однако техническая реализация устройств для расшифровки номеров линий не обеспечивает необходимого переходного затухания между выходами распределителя.

Наиболее близким техническим решением к изобретению является распределитель адреса линий для автоматических систем коммутации, содержащий пересчетную схему, например, в виде последовательно соединенных трех кольцевых регистров, и логический блок

И.

Известный распределитель имеет недостаточную величину переходного затухания сканируемых линий логического блока.

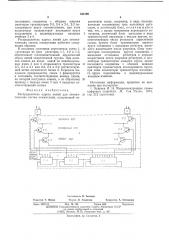

С целью повышения переходного затухания в предлагаемом распределителе адреса линий для автоматических систем коммутации логический блок выполнен в виде транзисторной пирамиды с числом ярусов, соответствующих числу регистров пересчетной схемы, причем базы транзисторов первого яруса соединены с выходами регистра, имеющего наименьшее число разрядов, базы транзисторов последующих ярусов соединены с выходами осталь5 ных регистров в порядке возрастания числа разрядов регистров, а коллекторы транзисторов каждого яруса, кроме последнего, соединены с общими шинами эмиттеров транзисторов последующего яруса, при этом коллектоIO ры транзисторов последнего яруса подключены к индивидуальным входным ячейкам.

На чертеже приведена структурная электрическая схема предложенного распределителя.

15 Распределитель адреса линий для автоматических систем коммутации содержит пересчетную схему 1, например, в виде последовательно соединенных трехкольцевых регистров 1-1, 1-2, 1-3, логический блок 2, выпол21 ненный в виде транзисторной пирамиды с числом ярусов, соответствующих числу регистров пересчетной схемы 1, причем базы транзисторов 2-5 и 2-6 первого яруса соединены с выходами регистра 1-1, имеющего наимень25 шее число разрядов, базы транзисторов 2-3, 2-4 и 2-1, 2-2 последующих ярусов соединены с выходами остальных регистров 1-2 и 1-3 соответственно в порядке возрастания числа разрядов регистров, а коллекторы транзисто30 ров 2-5, 2-6 и 2-3, 2-4 каждого яруса, кроме

543198 ресчетную схему, например, в виде последовательно соединенных трех кольцевых регистров, и логический блок, отличающийся тем, что, с целью повышения переходного за5 тухания, логический блок выполнен в виде транзисторной пирамиды с числом ярусов, соответствующих числу регистров пересчетной схемы, причем базы транзисторов первого яруса соединены с выходами регистра, имею10 щего наименьшее число разрядов, базы транзисторов последующих ярусов соединены с выходами остальных регистров в порядке возрастания числа разрядов регистров, а коллекторы транзисторов каждого яруса, кроме

15 последнего, соединены с общими шинами эмиттеров транзисторов последующего яруса, при этом коллекторы транзисторов последнего яруса подключены к индивидуальным входным ячейкам.

Источники информации, принятые во внимание при экспертизе:

1. Букреев И. Н. Микроэлектронные схемы цифровых устройств. М. Сов. Радио, 1973, 25 стр. 212 (прототип).

t — ) Составитель О. Тихонов

Техред Л. Гладкова

Редактор Т, Якова

Корректор А. Степанова

Заказ 3097/12 Изд. № 139 Тираж 869 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 последнего, соединены с общими шинами эмиттеров транзисторов 2-3, 2-4 и 2-1, 2-2 последующего яруса соответственно, при этом коллекторы транзисторов последнего яруса подключены к индивидуальным входным ячейкам 3 и 4.

Распределитель адреса линий для автоматических систем коммутации работает следующим образом, В исходном состоянии пересчетная схема 1, состоящая из трех регистров 1-1, 1-2 и 1-3, обеспечивает последовательный циклический обход линий закрепленной группы. При наличии заявки на входе одной из индивидуальных ячеек 3 или 4 открываются транзисторы

2-5, 2-3 и 2-1 или 2-6, 2-4 и 2-2 соответствующей ветви логического блока 2. Передача импульсов прекращается, схема 1 фиксируется в состоянии, соответствующем номеру линии, по которой поступила заявка, а по обратному проводу с выхода ячеек 3 или 4 выдается соответствующий сигнал.

Формула изобретения

Распределитель адреса линий для автоматических систем коммутации, содержащий пе! ! ! ! ! ! ! ! !

1 ! ! ! !