Цифровое сглаживающее устройство

Иллюстрации

Показать всеРеферат

в еи т е+.1-; - ° -, О Л ЭГС А Н И Е

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик (11) 543944

К ASYQPCNOMV СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 13.01.75(21) 2096588/24 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.01.773»оллетень № 3 (45) Дата опубликования описания 11.05.77 (51) М. Кл."ч 06 Р 15/34

Гасударственный комитет

Совета Министров СССР па делам изобретений и открытий (53) УДК 681.325 (088.8) (72) Авторы изобретения

Л. И. Сулин, Н. Н. Немшипов и К. П. Бочаров (71) Заявитель (54) ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к специапизиро»ванным средствам вычиспитепьной техники и может быть использовано дпя линейного преобразования сигнала.

HaBecòío цифровое сгпаживаюшее уст - 5 ройство, содержащее запоминаюшие бпоки, адресные блоки, счетные регистры, блоки управпения и сглаживаюший блок fl).

° Недостатком данного устройства явпяет ся низкое быстродействие и большой объем оборудования.

Наиболее близким по техническому решению к предлагаемому является цифровое сглаживаюшее устройство, выполняющее дискретное пинейное преобразование сигна«(5 ла в соответствии с соотношением

% Ä (n7)=Z Чl (n-»)Т A„>7. Ю,„(t)-j)7 В Щ алых,, т»х» ., ъых т.е. устройство, функция передачи которого go в z -области изображается в виде к-»

X. А„z

»=о -у g..z

1» 25

2 где 4>> %вы„- выборки входного и выходного сигналов

Т вЂ” период дискретизации сигнала

N — число входных выборок, принимаюших участие в преобразовании;

М - число выходных выборок принимаюших участие в преобразовании

А Q — коэффициенты (2) .

Йпя ввода сигналов в цифровые схемы используют их дискретизацию по времени и уровню, применяя для этой пели аналогоцифровые преобразоватепи.

Хранение коэффициентов А„ В » а также задержка выборок сигналов в таких устрой ствах осушествпяются в блоке памяти, а умножение и спожение — в арифметических блоках, построенных в виде цифровых логических схем.

Устройство (1) содержит запоминаюший блок, состоящий из накопителей входных и выходных выборок, разряды которыхобьединены цепями сдвига, блок памяти коэффициентов, лт сумматоров единиц, f77 разрядных накопителей выходной сумматор-накопитель и элементы И по числу выборок. Недостатком

543944 данного устройства является его сложность и низкое быстродействие.

Бель изобретения — сокращение оборудования и повышение быстродействия устройства за счет совмещения функций хранения выборок с их обработкой в специальном. запоминающем блоке.

Поставленная цель достигается за счет того, что в устройстве выходы одноименных разрядов накопителей выборок через сумматоры единиц соединены с соответствук шими разрядными накопителями, младшие разряды которых соединены с входами выходного сумматора-накопителя, а все ðàçряды объединены цепями сдвига, шины считывания накопителей выборок соединены с выходами элементов И, первые входы которых соединены с шиной тактовых импуль сов, а вторые — с выходами блока памяти коэффициентов, входы накопителя входных 26 выборок являются входом устройства, а входы накопителя выходных выборок соединены с выходами сумматора-накопителя, являющимися выходами устройства.

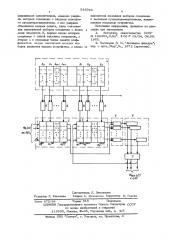

На чертеже изображена блок хема пред 25 лагаемого устройства.

Устройство содержит запоминающий блок

1, накопитель 2 входных выборок, накопитель

3 выходных выборок, блок 4 памяти коэффициентов, сумматор 5 единиц, разрядный накопитель 6, выходной сумматор-накопи« тель 7, элемент И 8.

Все ячейки памяти накопителей входных и выходных выборок соединены друг с другом цепями сдвига.

Коэффициенты А и В хранятся в блоке 4 памяти коэффициентов, ячейки памяти которого выполнены в виде Тп -разрядных сдвиговых регистров, каждый из которых замкнут в кольцо.

Устройство работает следующим образом. ,Очередная выборка сигнала с выхода

А1ЛП поступает в первую ячейку накопителя 2, а образованная в выходном сумматоре-накопителе 7 выходная выборка - в пер45 вую ячейку накопителя 3, причем все остальные хранимые в этих массивах выборки сдвигаются, выталкивая в каждом массиве последнюю выборку, В исходном состоянии коэффициенты А. и В> располагаются в регистрах памяти блока 4- памяти коэффициентов так, что в первых разрядах этих регистров находятся младшие разряды коэффициентов.

Формирование выходной выборки сигнала осуществляется за п циклов, каждый из которых состоит из трех тактов.

Первым тактовым импульсом одновременно опрашиваются входы всех элементов И. Сигналы считывания появляются

1 на выходах тех элементов И, которым соответствуют единицы в опрашиваемых разрядах коэффициентов А и Вj .

Выходные сигналы, образующиеся при чтении одноименных разрядов блока 1, поступают на соответствующие входы сумматоров

5 единиц, которые преобразуют количество прочитанных единиц в числа разрядностью Го (.Полученные числа отправляются в накопители 6.

Во втором такте m -разрядное число, образованное младшими разрядами разрядного накопителя 6, складывается с содержимым выходного сумматора-накопителя 7, В третьем такте производятся сдвиги на один разряд содержимого накопителей 7 и 6 в сторону младших разрядов, а также циклический сдвиг на один разряд всех коэффициентов в регистрах памяти блока 4 памяти коэффициентов. При этом, в первых разрядах регистров памяти оказываются сле» дующие по весу разряды коэффициентов А и В, После завершения гй таких циклов в выходном. сумматоре-накопителе 7 образует» ся выходная выборка сигнала. В дополнительном (3ttt + 1) такте эта выборка поступает в первую ячейку накопителя 2 после сдвига всех выборок в этом массиве на один шаг вправо. Одновременно таким же образом производится ввод новой входной выборки.

Таким образом, минимальный период Т получения выходных выборок определяется временем выполнения (З п + 1) описан» ных выше тактов.

Уменьшение стоимости цифрового сглаживающего устройства за счет сокрашения оборудования и однородности его структуры позволяет применять его на больших интегральных схемах.

Формула изобретения цифровое сглаживающее устройство для линейного преобразования сигнала, представленного временными выборками в виде тп -разрядных двоичных чисел, содержащее запоминающий блок, состоящий из накопителей входных и выходных выборок, разряды которых объединены цепями сдвига, блок памяти коэффициентов» W сумматоров единиц

m разрядных накопителей, выходной сумматорнакопитель и элементы И по числу выборок

Ф о т л и ч а ю ш е е с я тем, что, с целью сокрашения оборудования и увеличения быстродействия устройства, выходы одноименных разрядов накопителей выборок через сумматоры единиц соединены с соответствуюши;ми

543944

10 р

Вм

4о г Аида и- а> вд

W@ (ef пт Аип ьм (пт) к ЦАП

Составитель Л, Захматова

Редактор Г. Киселева Техред А. Демьянова Корректор И. Гоксич

Заказ 872/64 Тираж 818 Подписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб„д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 разрядными накопителями, младшие разряды которых соединены с входами выходно»

ro сумматора-накопителя, а все разряды объединены цепями сдвига, шины считывания накопителей выборок соединены с выходами элементов И, первые входы которых соединены с шиной тактовых импульсов, а вторые — с выходами блока памяти коэффициентов, входы накопителя входных выборок являются входом устройства, а входы накопителя выходных выборок соединены с выходами сумматора-накопителя, являющимися выходами устройства.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 192493 М.Кл . ф 06 F 15/34, 04,08.

1965, 2. Хьюлеман Л. П,, "Активные фильтры" пер. с англ.,Мир,М„1972 (прототип).