Многоканальный коммутатор для системы передачи информации

Иллюстрации

Показать всеРеферат

Сювз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСХОМХ СВИДЕТБДЬСТВХ (ii) 543972 (6}) Дополнительное к авт. свид-ву (22) Заявлено30.07.75 (2!) 2164508/24 с присоединением заявки №(23) Приоритет(43) Опубликовано25.01.77.Бюллетень № 3 (45) Дата опубликования описания 21.03.78 (Я) .ц. Кл.

Q 08 С 15/06

Государственный номнтет

Соввта Миннотроа СССР

IIo делам нэсоретеннй н аткрытнй (53) УДК 621.398 (088. 8) (72) Авторы изобретения В.В. Федоров, Г.А. Смирнов и А.A. Калачева (71) Зайвитель Ленинградский институт авиационного приборостроения (54) МНОГОКАНАЛЬНЫЙ КОММУТАТОР ДЛЯ СИСТЕМЫ

ПЕРЕДАЧИ ИНФОРМАЦИИ

Изобретение относится к системам передачи электрических сигналов с передачей сигналов в импульсной форме и предназначено для твлеметрических систем, для систем массового обслуживания и автомати- 5 ческих систем управления АСУ, в том чис,ле для систем управления производством.

Известны многоканальные коммутаторы, предназначенные для ациклической коммута ции управляемых объектов, которые содер- l0 жат электромеханические переключающие устройства с набором контактов, предварительно закоммутированные на управляемые .объекты. Коммутация в них осуществляется путем механического перемещения контак- 15 тов в шаговых переключателях или кодирующих дисках, что определяет низкое быст родействие и невысокую надежность. Кроме

:того, рассматриваемые коммутаторы имени ограниченные функциональные возможности, большие габариты, вес и потребляемую мощность иэ-за наличия механических приводов (1).

Из известных многоканальных коммутаторов в адаптивных телеметрических системах наиболее близким по технической сущности к предлагаемому является многоканальный коммутатор для системы передачи информации, содержащий блок управления, выход которого соединен через элемент задержки с входом блока, пересчета, блок памяти и де ,шифратор (2).

Блок пересчета формирует коды моментов опроса датчиков, каждому дискретному .моменту времени t: „соответствует двоич,ное слово, состоящее из слогов. B блок па мяти поступают отдельные слоги двоичного .слова, т.е. относительные адреса вго ячеек.

:Блок памяти имеет списковую структуру, которая строится заранее в процессе составления программы измерений. Дешифратор осуществляет преобразование кодового пред- . ставления номера опрашиваемот о датчика в пространственное.

Блок управления синхронизирует работу других блоков по тактам, в каждый из которых происходит обращение к блоку памяти для нахождения некоторого элемента .списка, .543972

Основными недостатками данного коммун татора являет "я нвакое быстродействие и сложность коммутатора, что объясняется введением блока памяти, имеющим списко вую структуру, и тем, что нахождение истинного адреса каждого элемента определи» ется суммированием базового адреса, найденного в предыдущем такте работы устройства с относительным адресом этого элемента, который указан в соответствующем; ð слоге выходного слова блока пересчета.

Цель изобретения — повышение быстро.действия многоканального коммутатора.

Поставленная цель достигается тем, чтф в него введены регистр состояния на триг 1к герах, единичные входы которых обьедине ны в группы, блок сквозного переноса, вы- полненный из последовательно соединенных по первому входу элементов И, и блок групповогс восстановления, выполненный из последовательно соединенных по первому входу элементов И, обьединенных в группы соответственно частоте коммутации, вторь1е входы которых подключены к нулевым выходам соответствующих разрядов блока пе- э5 ресчета, выходы групп элементов И блока, группового восстановления подключены к соответствующим группам единичных входов триггеров регистра состояния, выход бло ка управления соединен с входом блока груп-30 нового восстановления, выход элемента задержки подключен к первому входу первого элемента И блока сквозного переноса и к нулевому входу первого триггера регистра состояния, единичные выходы триггеров регист-85 ра состояния соединены с выходами многоканаль ного коммутатора, нулевые выходы триггеров регистра состояния подключены ко вторым входам соответствующего элемента И блока сквозного переноса, выход каждого 40 из которых соединен с нулевым входом последующего триггера регистра состояния.

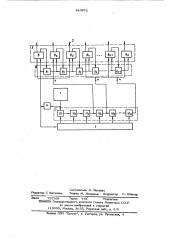

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит блок управления 1, 45 блок пересчета 2, входы 3 датчиксв, выходы

4 блока группового восстановления, соответ ствующие частоте коммутации1регистр состояния 5, блок сквозного переноса 6, блок группового восстановления 7, триггеры 8 - 50

8п, элементы И 9 - 9„< элементы И

10< - 10»„, элемент задержки 11.

Многоканальный коммутатор для системы передачи информации работает следующим образом. М

В исходном положении все триггеры 8 коммутатора находятся в нулевом состоянии. Первый импульс генератора тактовых импуль1 сов блока управления 1 поступает на вход ,блока группового восстановления 7 и устайавливает триггеры всех частотных групп регистра состояния 5 в единичное положение. Тот же импульс через элемент задержки 11 опрокидывает гервый триггер 8 блока 5 в нулевое состояние, что обеспечивает опрос соответствующего этому триггеру датчика, подключенного к триггеру 84. Одновременно начинает работать блок пересчета 2.

Следующие тактовые импульсы вызывают последовательное переключение триггеров блока 5 с помощью блока сквозного пе- реноса 6, что обеспечивает последовательный опрос датчиков, подключенных к выходу многоканального коммутатора до тех пор, пока блок пересчета 2 не насчитает число импульсов, равное гериоду опроса датчика самой высокочастотной группы. Далее от очередного тактового импульса срабатывает спок группового восстановления 7, что выаывает переключение триггеров первой частотной группы в единичное состояние.

Следующее срабатывание блока группово., го восстановления 7 произойдет тогда, ко да блок пересчета 2 насчитает количество тактовых импульсов, равное периоду опроса датчиков второй частстной группы. При этом произойдет восстановление триггеров первой и второй частотных групп в единич ное состояние и так далее, пока через пе-. риод опроса самого низкочастотного датчи« ка не произойдет восстановление триггеров. всех частотных групп регистра состояния

5, flanee цикл работы блока группового восстановления 7 повторяется. После каждого срабатывания блока группового восстановления опрос датчиков начинается с самой высокочастотной pynmû.

В предлагаемом устройстве время коммутации определяется следующим образом:

Г t к зосст опроса где t - время срабатывания блока группового восстановления 7 и регистра состояния; время работы регистра состояния 5 сводится ко времени переключения триггера, а время сра- батывания блока группового восстановления 7 может быть сведено ко времени работы одного элемента И (7и );

- время срабатывания регистра состояния 5 и блока сквозного переноса 6, которое может быть определено време- нем срабатывания триггера и временем срабатывания блока сквозного переноса.

Время же работы известного многоканаль. ного коммутатора определяется быстродей543972 с1вием оперативного запоминающего устрой ства {ОЗУ) и арифметического устройства, формирующего исполнительные адреса ОЗУ, Времй коммутации одного объекта вкпючает в себя нескопько обращений к ОЗУ и несколь- б ко операций сложения дпя отыскания базового адреса в памяти. Сюда же входит время срабатывания блока пересчета и дешифратора кодов, что на порядок превышает время срабатывания предлагаемого многоканапьного коммутатора даже при испопьзовании самых быстродействующих современных элементов.

Данный коммутатор также обеспечивает упрощение б66к-схемы иэ-эа отсутствия спож-)й ного ОЗУ, обьем которого в ячейках значи« тельно больше количества коммутируемых объектов, тогда как в предпагаемом комму-, таторе на каждый опрашиваемый обьект рааходуется один триггер регистра состояния, ЯФ кроме того, в предлагаемом коммутаторе отсутствуют такие сложные элементы, как дешифратор и суммирующие устройства дня формирования испо нителыых адресов опе ративного запоминающего устройства. 35

Формупа изобретения

Многоканальный коммутатор ддя системы 30 передачи информации, содержащий блок уп равления, выход которого соединен через элемент задержки с входом бпока пересче та,отличающийся тем,что,с целью повышения быстродействия многока. 85 нального коммутатора, в него введен регистр состояния на триггерах, единичные входЫ которых обьединены в группы, блок сквоз- ного переноса, выполненный иэ последовательно соединенных по первому входу элементов И, и блок группового восстановления, выполненный из последовательно соединенных по первому входу элементов И, объединенных в группы соответственно частоте коммутации, вторые входы которых подкФочены к нулевым выходам соответствующих разрядов блока пересчете, выходы групп элементов И блока группового восстановле ния подключены к соответствующим группам единичных входов триггеров регистра состояния, выход бпока управления соедияен с входом блока группового восстановления, выход элемента задержки подключен, к первому входу первого элемента И блока сквозного переноса и к нулевому входу пер

Мого триггера регистра состояния, единич ные выходы триггеров регистра состояния, соединены с выходами многоканального коммутатора, нупевые выходы триггеров регистра состояния иодключены ко вторым входам соответствующего элемента И блока сквоз. ,ного переноса, выход каждого из которых соединен с нулевым входом последукицего

1григгера регистра состояния.

Источники информации, принятые во вни. мание при экспертизе;

1. Авторское свидетепьство СССР

Ж 454708, М.Кл . @ 08 С 19/16, 01.

1 0.72.

2. Авторское свидетельство СССР

Q 299864, М,Кл . Я 08 С 19/16, 23.03.71 (прототип) .

543972

Составитель Н. Лысенко

ТехРед М. Левицкан Корректор С. Шекмар

Редактор Г. Киселева

Филиал ППП "Патент, г. Ужгород, ул, Проектная, 4

Заказ 75 7/65 Тираж 7 78 Подписное

ЯНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

L j.3035, Москва, Ж-35, Раушская наб., д. 4/5