Устройство для умножения частоты следования периодических импульсов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДИТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву№ 357668 (22) Заявлено 01.12.75 (21) 2193594/21 с присоединением заявки № (23) Приоритет— (43) Опубликовано 25.01,77.Бюллетень № 3 (45) Дата опубликования описания 07.05.77

Соеоз Советских

Социалистических

Республик (11) 544112 (51) М. Кл

Н 03 К 5/01

Государственный камитет

Совета Министров СССР ао делам изобретений и аткрытий (53) УДК 621 374 4 (088.8) (72) Авторы изобретения

T. М. Алиев и А. P. Салаев (71) Заявитель

Азербайджанский институт нефти и химии им. М. Азизбекова (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧАСТОТЫ

СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ

Изобретение относится к автоматике и измерительной технике и может быть использовано в цифровых измерителях частоты.

Известно устройство для умножения частоты следования периодических импульсов, содержашее делитель опорной частоты, с ко эффициентом деления, равным коэффициенту умножения, счетчик импульсов опорной частить":, счетчик импульсов, формирователь, зацоминаюший регистр, два блока переноса, 0 построенных на схемах И и блок управления.

Однако этo устройство характеризуется погрешностью дискретности, обусловленную некратностью числа М импульсов генератора опорной частоты т «, поступаюших в те-15 чение периода Т„умножаемой частоты У,< на вход делителя, коэффициента К деления.

В результате к конту каждого периода

Тхв делителе может остаться число, пред- 20 ставляюшее дробную часть частного от деления г1/ K что выражается в погрешности периода следования импульсов выходной последовательности, достигаюшей в пределе величины Т 25

Целью изобретения является повышение тоЧности умножения.

С этой целью в устройство для умножения, содержашее делитель опорной частоты с коэффициентом деления, равным коэффициенту умножения, счетчик импульсов опорной частоты, формирователи, запоминаюший регистр, два блока переноса и блок управления, введены дополнительный блок переноса, дополнительный запоминающий регистр, дешифратор, апементы совпадения, линии задерж ки, элемент ИЛИ и логическое устройство, состояшее из триггера и элементов И, первые входы которых подключены к источнику опорной частоты, вторые входы — к выходам триггера, первый вход которого соединен с выходом входного формирователя, а второй вход — с одним из выходов блока управления, другие выходы которого подключены ко входам дополнительного блока переноса и дополнительного запоминаюшего регистра, причем выход одного из элементов И подключен ко входу блока управления, а выход второго — ко входу делителя опорной частоты, единичные выходы которого через дополннтельный блок переноса и дополнительный запоминающий регистр, которые соединены последовательно, подключены ко входам дешифратора,; при этом выходы дешифратора сое.динены с первыми входами элементов соила- 5 денни, вторые входы которых объединены и подключены к выходу выходного формирователя, выход перво о непосредственно, а выходы остальных через линии задержки под-, ключены ко входам элемента ИЛИ. 10

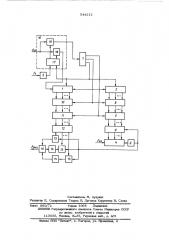

На чертеже представлена структурная электрическая схема устройства для умноже- ния частоты следования периодических импульсов.

Устройство содержит делитель 1 опорной 15 частоты с коэффициентом деления К, счет- чик 2 импульсов, образуемых при делении опорной частоты, входной формирователь 3, счетчик 4 импульсов опорной частоты, запо.минающий регистр 5, выходной формирова-. 29 тель 6, блок 7 управления, .блоки 8 и 9 переноса кодов, построенные на логических элементах И, дополнительный блок 10 переноса кодов, дополнительный запоминающий регистр: 11, дешифратор 12 pлeмeнть сов- 25 падения 13, лидии задержки 14, элемент

ИЛИ 15, логический элемент 16, состоящий из триггера 17 и элементов И 18 и 19.

Устройство работает следующим образом.

Каждый импульс умножаемой частоты 1, ЗО через входной формирователь 3 поступает ,на нулевой вход триггера 17, который, перебрасываясь, открывает элем нт И 19 для прохождения импульсов опорной частоты У на вход блока 7. За время поступления в блок 7 импульсов частоты Уол в этом бло ке вырабатываются три сигнала, первый из .которых устанавливает в О" все разряды запоминающих регистров 5 и 11, второй поступает на вторые входы схем И блоков

Я и 10 и переносит обратный код из счетчика 2 в запоминающий регистр 5 и прямой код из делителя 1 в запоминающий регистр

11, третий устанавливает все разряды счетчика 2 в состояние "1" и записьвает в "5 делителе 1 число, равное количеству импульGoB частоты Eon прошедших на вход блока

7. Одновременно третьим сигналом из блока

7 перебрасывается триггер 17 и открывается элемент И 18 для прохождения импульсов Родна вход делителя 1.

Импульсы с выхода делителя 1, частота следования которых равна toК,>

HQ вход счетчика 2 поступает число импульсов равное Т„ х kò„n

Прп этом и делителе 1 к концу периода Т, образуется остаточное число m обусловлен- О ное некратностью числа N импульсов опор ной частоты, поступивших на вход делителя, коэффициенту К (щ «с K)

Поскольку все разряды счетчика 2 предварительно были установлены в 1, то в счетчике 2 фиксируется число, равное И„-k.

Это число после поступления очередного импульса умножаем ой частоты сигналом из блока 7 переносится в обратном коде посредством блока 8 в запоминающий регистр 5 и, таким образом, в регистре 5 устанавливае ется дополнительный код числа Й „. Одновременно этим же сигналом из блока 7 переносится остаток m из делителя 1 в запоми-, нающий регистр 11.

Импульсы опорной частоты непрерывно поступают на вход счетчика 4. Каждый импульс переполнения с выхода счетчика 4 через выходной формирователь 6 поступает на вторые входы элементов И блока 9, посредством которых осуществляется перенос дополнительного кода числа М х из запоминающего регистра 5 в счетчик 4. В резуль-тате на выходе выходного формирователя 6 образуется последовательность импульсов с периодом следования.

T=N Т

on

Однако s действительности период Т оказывается меньше, чем определяется остаточным числом " N " в делителе 1. В пределе это уменьшение составляет величину Т„, и, таким образом, с учетом максимальной погрешности дискретности, выражение для периода следования на выходе выходного формирователя 6 запишется

Т ==Т тх оп

Для уменьшения погрешности дискретности сигнал с выхода выходного формирователя 6 подается на один из входов элементов совпадения 13, другие входы которых соединены с соответствующими выходами дешифратора 12, Дешифратор 12 анализирует состояние запоминающего регистра 11 и в зависимости от числа " т " выдает разрешающий потенциал на первый вход соответствующего элемента совпадения 13. Число выходных шин дешифратора 12 определяется тем, во сколько (fl раз) требуется уменьшить погрешность дискретности. При этом, если число t7)(то разрешающий потенциал поп является на первом входе того элемента совпадения 13, выход которого непосредственно связал со входом элемента ИЛИ 15. При иW (2- разрешающий потенциал появляк. к и ется на шине дешифратора 12, связанным с перв и м вх од ом элемента с овпадения 1 3, выход которого соединен со входом элемен5

+ ИЛИ 15 через линию задержки 14 со вре;ене; за е жки 1, =, при 2 л < п С

° 11 К соединение со входо элемента ИЛИ 15 про ъ оп

:"сход .:.т через линию задержки 14 с Т-" 2-„

К прн Ъ д c pl < 4 > через линию задержки 14 с

t-Ъ 5" и т.д.

Таким образом, если сигнал с выходе формирователя 6 подать на вторые входы элементов совпадения 13, то период его поЬторения на выходе элементе ИЛИ 15 будет щ с учетом; максимальной погрешности дискреМности определяться выражением õ 1он аых К, г,е. максимальная погрешность дискретности уменьшается в " n раэ. При этом увеличивается стабильность коэффициента умножения, уменьшается фазово-импульсная модуляция выходного сигнала и расширяется рабочий диапазон частот. действительно, ус.» ловие отсутствия перескоков коэффициента ,умножения К запишется в виде:

25, откуда оу

Х g -K

Последнее выражение интерпретируется сле дующим образом;

1. Диапазон умножаемой частоты yaenw з .<ивается в ">" раэ, 2. При сохранении У„возможно в "и ., аз уменьшить Уо,, (уменьшить быстродей,твие счетчиков) или соответственно увели

40, :ить коэффицчент умножения.

Выражение для максимально возмож.::-:сй нестабильности фазы выходных импульсов умнсжителя запишется в виде (в радианах)

2 <р--.2р 1 х т.е. фаэово-импульсная модуляция выходного сигнала уменьшается в rl раэ.

Формула изобретения

Устройство для умножения частоты сле.дования периодических импульсов, по авт. св. ¹ 357668, о т л и ч а ю щ е е с я тем, что, с целью повышения точности умножения, в него введены дополнительный блок переноса, дополнительный запоминающий регистр, дешифратор, элементы совпадения, линии задержки, элемент ИЛИ и логическое устройство, состоящее из триггера и элементов И, первые входы которых подключены к источнику опорной частоты, вторые входы к выходам триггера, первый вход которого соединен с выходом входного формирователя, а второй вход — с одним из,выходов блока управления, другие выходы которого подключены ко входам дополнительного блока переноса и дополнительного запоминающего регистра, причем выход одного из элементов

: И подключен ко входу блэка управления, а вы:;ход второго — ко входу делителя опорной часто ты, единичные выходы которого через дополнительный блок переноса и дополнительный запоми: нающий регистр, которые соединены последова:,тельно, подключены ко входам дешифратора при этом выходы дешифратора соединены с

;первыми входами элементов совпадения, вто-, рые входы которых объединены и цодключе.ны к выходу выходного формирователя, вы"ход первого непосредственно, а выходы ос1

:тальных через линии задержки подключены ко входам элемента ИЛИ.

544112

Составитель М. Аудрииг

Редактор Е. Скляревскаа Техред О, Луговая Корректор В. Салка

Заказ 960/71 Тираж 1065 Подписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, -35, Раушскаи наб., д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4