Цифровой фазовращатель

Иллюстрации

Показать всеРеферат

Е <» в441гв

Социалистииеских

Республик

ИЗОБРЕТЕН ИЯ

К ABfOPCKOMV СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 20.05.75 (21) 2135905/24 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.01.77.Бюллетень ¹ 3 (45} Дата опубликования описания 10.05.77 (51) М. Кл,"Н 03 К 13/02

Государственный комитет

Совета Министров СССР оо делам изооретеннй и открытий (53) УДК 621.314 (088.8 ) 72) Автор изобретения

В. М. Воина (71) Заявитель (54) БИФРОВОЙ ФАЗОВРАЩАТЕЛЬ 1 z

Х+- -- =Х н) и

1 т,- т

Союз Советских 1

Изобретение относится к автоматике и предназначено для дискретного изменения фазы входного сигнала.

Известен фаз оврашатель, п остр оенный на осн ове цифр ов эг о распределителя, в к от ор о м уменьшение дискрета фазы достигается за счет изменения месторасположения, длительности и амплитуды импульсов, формирующих ступенчатую структуру jl) . Плошадь каждой "ступеньки" определяет весовое зна- ip чение соответствующего разряда, à смешение одной "ступеньки" относительно другой к оси времени позволяет изменять фазовый сдвиг первой гармоники, выделяемой фильтром из ступенчатого сигнала, (Л

Однако известный фазоврашатель не обеспечивает достаточной точности.

Известен также цифровой фазоврашатель, содержаший генератор импульсов, подключен- 2р ный ко входу делителя частоты, выходы которого соединены с одними входами блоков сравнения кодов, и преобразователь кода(2).

Такой фазовращатель также не обеспечивает достаточной точности.

Белью изобретения является повышение точности фазоврашателя.

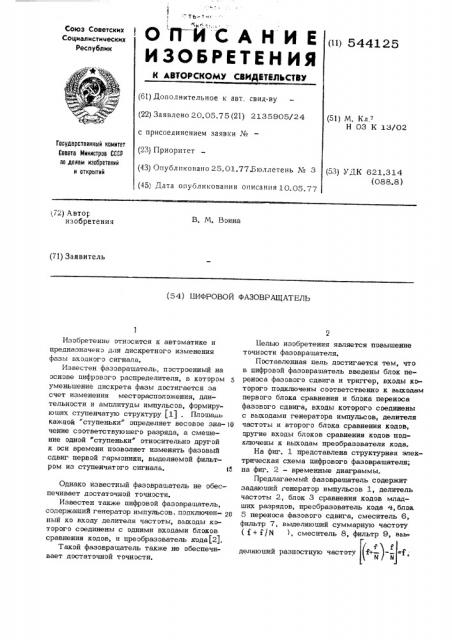

Поставленная цель достигается тем, что в цифровой фазоврашатель введены блок переноса фазового сдвига и триггер, входы которого подключены соответственно к выходам первого блока сравнения и блока переноса фазового сдвига, входы которого соединены с выходами генератора импульсов, делителя частоты и второго блока сравнения кодов, цругие входы блоков сравнения кодов подключены к выходам преобразователя кода.

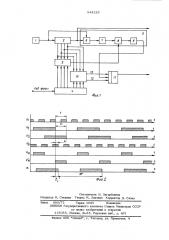

На фиг. 1 представлена структурная электрическая схема цифрового фазоврашателя; на фиг. 2 — временные диаграммы.

Предлагаемый фазоврашатель содержит задающий генератор импульсов 1, делитель частоты 2, блок 3 сравнения кодов младших разрядов, преобразователь кода е, блок

5 переноса фазового сдвига, смеситель 6, фильтр 7, выделяющий суммарную частоту (f + Е / N ), смеситель 8, фильтр 9, вьь« деляюший разностную частоту

544125 блок 10 сравнения кодов старших разрядов (— К ) — ый триггер 1 1.

Парафазные выходы 12 и 13 блока 10 сравнения кодов старших разрядов соединены с входами триггера 11.

Рассмотрим работу устройства по временным диаграммам, представленным на фиг. 2.

С выхода генератора импульсов 1 поступает импульсная последовательность Б периодом Т = i/f . Эта последовательность пос-10 тупает на опорный делитель частоты 2, на выходе которого имеем последовательность

U с частотой f/ N В результате сравнения разрядов опорного делителя 2 и младших разрядов преобразователя кода 4 на вы- 5 ходе блока 3 сравнения кодов младших разрядов имеем импульсную последовательность )З, сдвинутую на угол ф, относительно сигнала U на выходе опорного делитеа ля частоты 2. Минимальная величина фазового сдвига равна

pili где Й вЂ” коэффициент деления опорного делителя. 25

С помощью блока 5 переноса фазового сдвига угол переносится на высокую частоту, и на выходе фильтра 9 имеем импульсную последовательность Ц, сдвинутую на

) угол р относительно сигнала U . Вре>

3. мя задержки (опережения) 6 импульсов U относительно U определяется из

9 известных соотношений

2й > 9Т ч> = — 6

Х Т 4) i 2В Э5 !

Определим сини

= — °

T я и

На выходах блока 10 сравнения кодов старших разрядов имеем две импульсные последовательности U,, U частотой

1 ш

Г/N (периодом N Т), сдвинутые одна относительно другой на 180, сдвигаемые синхронно относительно сигнала на выходе опорного делителя частоты 2, в соответствии с кодом старших разрядов преобразователя кода 4.

Допустим, расположение импульсов U, тъ 50 и й, соответствует нулевому значению фазы. Определим в этом случае минимальный

4 фазовый сдвиг на выходе () — К)-го триггера 11 — U относительно сигнала на выи ходе эпорного делителя частоты 2.

Очевидно

2п — 1

Аналогичным образом можно увеличить число ступенек задания фазового сдвига, минимальный фазовый сдвиг в этом случае определится формулой:

2 В 1и = где k — число ступеней задания фазы.

Таким образом, в фазовращателе имеется возможность уменьшить дискретность задания фазы, не увеличивая коэффициент деления делителя и не уменьшая выходную частоту.

Дискрет фазы зависит только OT коэффициента деления делителя частоты Й и числа ступеней преобразования (, что выгодно отличает цифровой фазовращатель от аналогичных технических решений.

Формула из обретения

Цифровой фазоврашатель, содержащий генератор импульсов, подключенный ко входу делителя частоты, выходы которого соединены с одними входами блоков сравнения кодов, и преобразователь кода, о т л и ч а юшийся тем, что, с целью повышения точности фазовращателя, в него введены блок переноса фазового сдвига и триггер, входы которого подключены соответственно к выходам первого блока сравнения и блока переноса фазового сдвига, входы которого соединены с выходами генератора импульсов, делителя частоты и второго блока сравнения кодов, другие входы блоков сравнения кодов подключены к выходам преобразователя кода.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР а

No 229058, МКл Н 03 Н 7/18> опубликовано 1970.

2. Зверев А. Е. и др. Преобразователи угловых перемещений в цифровой код, Л., "Энергия, 1974., с. 133 (прототип).

544125

Составитель И. Загорбинина

Редактор О. Стенина Техред М. Ликович Корректор В. Салка

Заказ 960/71 Тираж 1065 Подписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4