Устройство управления перестройкой частоты

Иллюстрации

Показать всеРеферат

О П и С А Н и Е (11)544137

ИЗОБРЕТЕН ИЯ

Союз Советских

Социвлистинеских

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву(22) Заявлено 19 02,75 (21) 2106426/09 с присоединением заявки №(23) Приоритет— (43) Опубликовано 25.01.77, Бюллетень № 3 (45) Дата опубликования описания 05.05.77 (5i) М, Кл.Н 04 В 1/10

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.396.42 (088.8) (72) Автор изобретения

А, А. Козлов (71) Заявитель (54) УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕСТРОЙКОЙ ЧАСТОТЫ

Изобретение относится к системам связи и может использоваться в устройствах управления перестройкой частоты приемных и передающих устройств, в комплексах наклонного зондирования ионосферы и выбора оптимальных частот связи.

Известно устройство управления перестройкой частоты системы связи, содержащее последовательно соединенные коммутатор, декадный счетчик и схему сравнения, а так- ip же регистр, включенный между коммутатором и другим входом схемы сравнения, и шифратор )lj.

Однако в известном устройстве при приеме сигналов от нескольких передающих цент-15 ров возможны ошибки в перестройке частоты.

Цель изобретения — повышение точности перестройки при приеме сигналов нескольких передающих центров. 20

Для этого в предложенное устройство введены запоминающий блок, наборный блок, два распределителя, одновибратор, элементы

И и ИЛИ, при этом наборный блок через шифратор и запоминающий блок подключен к 25

KDììóòàòîðó,. выход ш .фратора подключен к другому входу коммутатора, к стробируюшим входам которого подключены выходы обоих распределителей, выход первого распределителя подключен к гервому адресному входу запоминающего блока, первый вход первого распределителя подключен к наборному блоку, другой выход которого подключен к первому входу переключателя, первый выход которого подключен к входу второго распределителя, а второй вход первого распределителя подключен к второму выходу переключателя, причем другие адресные входы запоминающего блока соединены с выходами элементов И, первые входы KQTopblx подключены к выходу элемента ИЛИ, один вход которого подключен к третьему выходу наборного блока, на другой вход элемента ИЛИ через одновибратор и на третий вход первого распределителя непосредственно поданы импульсы начала цикла, а на второй вход переключателя поданы импульсы тактовой частоты.

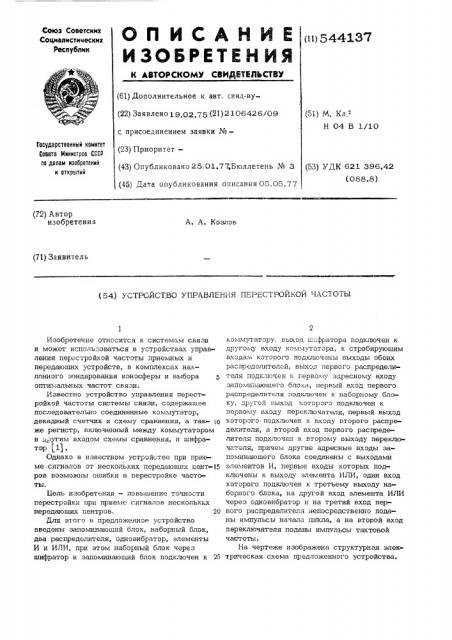

На чертеже изображена структурная электрическая схема предложенного устройства, 544137

Оно содержит последовательно соединенные коммутатор 1, декадный счетчик 2 и схему сравнения 3, регистр 4, вк;иэчеиный между коммутатором 1 и другим входом схемы сравнения 3, а также шифратор 5, запомпна|оший блок 6, наборный блок 7, распределители 8 и 9, элементы И 10 и элемент ИЛИ 11, одновибратор 12. При этом наборный блэк 7 через шифратор 5 и запоминающий блок 6 пэдключен к коммута- 10 тору- 1, выход шифратора 5 подключен к другому входу коммутатора 1, к стробируюU1HIv. входам которого подклочены выходы распределителей 8 и 9, при этом выход распределителя 9 подключен также к перво- 15 му адресному входу запомщгаюшего блока

6, первый вход распределителя 9 подключен к первому выходу наборного блока 7, второй выход которого подключен к первому входу перекшочателя 13, первый выход 2Е которого подключен к входу распределителя

8, а второй вход распределителя 9 подключен к второму выходу переключателя 13.

Причем другие адресные входы запоминающего блока 6 соединены с выходамп элементов И 10, первые входы которых подключены к выходу элемента ИЛИ 11, один вход которэгэ подключен к третьему выходу наборного блэка 7, на другой вход элемента ИЛИ

11 через эднэвибратор 12 и на третий вход ЗО растределителя 9 непосредственно поданы импульсы начала цикла, а на второй вход п реключателя 13 поданы импульсы тактовой частоты.

Устройство работает следующим образом

Для набора в запоминающий блок 6 начальных и конечных частот диапазона перестройки переключатель 13 ставится в положение

"Набор" При этом цепь сдвига распределитс— ля 8 отключается, а распределителя 9 подключается к наборному блоку 7. Переключа— тель 1 3 ставится в положение "1 . После этого с наборного блэка 7 в распределитель

9 записывается "1" и нажатием соответствующих кнопок производится набор частот.

При нажатии любой кнопки на вход запоминающего блока 6 с шифратора 5 поступает код соответствующей цифры, кроме того, в цепь сдвига распределителя 9 поступает продвигающий импульс, а на соответствующую координату запоминающего блока 6 через элемент ИЛИ 11 и один из элементов

И 10 поступает импульс опроса, С первого выхода распределителя 9 стробируюший им.пульс поступает на координату Х запоминаю-

1 щего блока 6 и на соответствующий вход коммутатора 1. При этом код первой цифры записывается в выбранный адрес запоминающего блока 6 и декаду счетчика 2, соответствующую старшему разряду частоты. При

60 нажатии кногки, соэтветствующей второй цифре набираемой частоты, единица" сдвигается в распределителе 9 на один разряд и кэд с выхода шифратора 5 записывается в адрес запоминающего блока 6 с координатой Х и в следующую декаду счетчика а

2, Пэ окончании набора начальной частоты диапазона набирается конечная частота, ког тэрая записывается пэ соответствующим адресам запоминающего блока 6 и в регистр

4. После этого переключатель 13 ставится; в положение, соответствующее второй программе, и набор повторяется Таким образом, гэ окончании процесса набора по соответствующим адресам запок.инающего блока будут записаны начальные и конечные частоты перестройки каждой программы. Пэсле зтого переключателем 13 выбирают нужную программу и ставят его в положение "работа", при этом цепь сдвига распределителя 9 подключается к цепи импульсов тактовой частэты, а распределителя 8 к наборному блоку 7.

Рассмотрим работу устройства в режиме зондирования. Импульсом начала цикла апускается одновибратор 12 v записывается "l" в распределитель 9. Однэвибратор

12 вырабатывает импульс, который через элемент ИЛИ 11 и соответствующий злемент

И 10 стробирует координату запом щающегэ блока 6, выбранную переключателем 1 3, иа время, превышающее цикл раооты распределителя 9. Импульсами тактэвэй частоты "1 " продвигается по распределителю

9 и стробирует координаты Х запоминающего блэка 6 и соответствующие входы коммутатора 1, при зтом в счетчик 2 записывается начальная частота диапазона зондирования, а в регистр 4 конечная частота. Б процессе перестройки счетчика

2 частота, получающаяся в нем, сравнивается схемой сравнения 3 с частотой, находяшейся в регистре 4. При совпадении этих частот схема выдает кэмаиду "Стоп", пэ которой гроцесс перестройки счетчика 2 прекращается. При поступлении следующего импульса начала цикла цикл работы повтор яется.

В режиме анализа начальная и конечная частота анализа набираются в счетчик 2 и регистр 4 соответственно пэсредствэм наборного блока 7, шифратора 5, комк утатэра

1 и распределителя 8, Запок1инаюший блок

6 и распределитель 9 при зтом в работе не участвуют.

Выполнение устройства в таком виде значительно повышает точность перестройкичастоты при приеме сигналов от нескольких передающих центров.

544137

11НИИПИ Заказ 793 /72 Тираж 872

Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Формула изобретения

Устройство управления перестройкой частоты системы связи, содержащее последовательно соединенные коммутатор, декадный счетчик и схему сравнения, а также регистр, включенный между коммутатором и другим входом схемы сравнения, и шифРатоР, отличающееся тем. что, с целью повышения точности перестройки при 10 приеме сигналов нескольких передающих центров, введены запоминающий блок, наборный блок, два распределителя, одновибратор, элементы И и ИЛИ, при этом наборный блок через шифратор и запоминающий блок подключен к коммутатору, выход шифратора подключен к другому входу коммутатора, к стрсбирующим входам которого подключены выходы обоих распределителей, выход первого распределителя подключен к первому адресному входу запоминающего блока, первый вход первого распределителя подключен к наборнс му блоку, другой выход которого подключен к первому входу переключателя, первый выход которого подключен к входу второго распределителя, а второй вход первого распределителя подключен к второму выходу переключателя, причем другие адресные входы запоминающего блока соединены с выходами элементов И, первые входы которых подключены к выходу элемента ИЛИ, один вход которого подключен к третьему выходу наборного блока, на другой вход элемента ИЛИ через одновибрачор и на третий вход первого распределителя непосредственно поданы импульсы начала цикла, а на второй вход переключателя поданы импульсы тактовой частоты.

Источник информации, принятый во внимание при экспертизе:

1. Отчет по ОКР "Сойка", инв . ¹ 07021 92, 1974 с. 43-45 (прототип).