Устройство для синхронизации двоичных сигналов

Иллюстрации

Показать всеРеферат

Союз Советских

Социвлистимеских

Республик

О П И С А Н И Е ()544162

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 11.09.75 (21) 2171184/09 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.01.77.Бюллетень Л" Э (45) Дата опубликования описания 16.05.77 (51) М. Кл.о

Н 04 I 7/10

Гасударственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621 394

662(088 8) (?2) Автор изобретения

В. П. Савин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ

ДВОИЧНЫХ СИГНАЛОВ

Изобретение относится к радиотехнике и может использоваться в системах связи, предназначенных цля перецачи дискретных сообщений, в телеграфии и в системах с импульсно-коцовой модуляцией. 5

Одно из известных устройств для синхронизации двоичных сигналов содержит делитель с добавлением с исключением импуль— сов, фазовый дискриминатор, выцелитель фронтов, накопительное устройство на базе 10 реверсивного счетчика цля повышения точности фазирования, и устройство переменного коррекционного эффекта для уменьшения времени вхождения в фазу (1).

Однако в известном устройстве накопителт чое устройство и коррекционное устройство управляются выхоцом фазового дискриминатора, опрецеляющим только знак фаз ов or о расс оглас ов а ни я без указания на его точное значение, что снижает быстро — 20 действие таких устройств.

Наиболее близким техническим решением является устройство для цвоичных сигналов, содержащее задающий генератор, выход которого поцключен к одному из входов делителя, к другому входу которого подключен вход вь:делителя фронтов сигнала (2)

Однако это устройство не обладает достаточной точностью и быстродействием фа— зирования.

Цель изобретения — повышение точности и быстродействия фазирования.

Для этого в устройство цля синхронизанции двоичных сигналов, содержащее задающий генератор, выход которого поцключен к одному из BxogoB делителя и к другому входу которого подключен вход выцелителя фронтов сигнала, введены сумматор, счетчик на вычитание, счетчик на сложение и дополнительный выцелитель фронтов, прн этом выходы"К разрядов делителя подключены к (l(+ N + 2) входам сумматора, выход последнего разряда которого поцключен к управляющему вхоцу целителя, а (k+ Ц выходы — к соответствующим входам счетчика на вычитание, к управляющему вхоцу которого подключен выхоц счетчика на сложение, а выход счетчика на вычитание через выделитель фронтов сигнала поцключен к входу "обнуление сумматора, уп—

544162 равляющий вход которого соединен со входом счетчика на сложение и с выходом цополнительнorо выделителя фронтов сигнала.

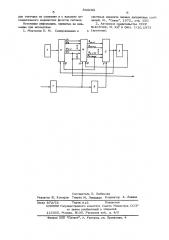

На чертеже представлена структурная электрическая схема устройства для синхронизации двоичных сигналов.

Устройство содержит задающий генера— тор 1, выхоц которого подключен к одному из вхоцов делителя 2, к другому входу ко- 10 торого подключен вход выделителя фронтов

3 сигнала, сумматор 4, счетчик на вычита— ние 5, счетчик на сложение 6, и дополнительный выделитель фронтов 7, при этом выходы (Q,-à„) "K" разрядов делителя 2 подключены 15 к (k rn 3 ) входам сумматора 4, выход(о„) последнего разряда которого подключен к управляющему входу 8 делителя 2, à (keg ) выходы (g - g 1-к соответствующим вхоlrl+1 k+l1lч дам счетчика на вычитание 5, к управляющему входу 9 которого подключен выход счетчика на сложение 6, а выход счетчика на вычитание 5 через выделитель фронтов

3 сигнала подключен к входу "обнуление"

10 сумматора 4, управляющий вход 11 ко- 25 торого соецинен со входом счетчика на сложение 6 и с выходом дополнительного выцелителя фронтов 7 сигнала.

Устройство работает следующим образом.

Последовательность высокочастотных импульсов с задающего генератора 1 поступает на счетный вход делителя 2 с коэффициентом деления "2 к„

С входа устройства на вход дополнительного выцелителя фронтов 7 поступает сигнал данных. Сигнал на выходе дополнительного выделителя фронтов 7 длительностью в один период высокочастотного колебания за- дающего генератора 1, определяющий значащий 4О момент сигнала данных, поступает на вход счетчика на сложение 6 и на управляющий вход

11 сумматора 4, Производится считывание двоичного состояния делителя 2 и сложение модифицированного обратного кода этого 45 состояния с содержимым сумматора 4.

В исходном состоянии .цикла накопленияусреднения содержимое сумматора 4 равно нулю. Счетчик на сложение 6 с емкостью

"2 " производит сложение поступающих на него импульсов с выхода дополнительного выделителя фронтов 7. При переполнении счетчика на сложение бимпульс с его выхода поступает на управляющий вхоц 9 счет- 5 чика на вычитание 5, и производит запись числа, равного усредненному значению фазового рассогласования эа цикл накопления, Счетчик на вычитание 5 имеет единственное устойчивое состояние — "нулевое".

При записи в него любого числа, отличного от нуля, он автоматически переходит в режим счета на вычитание. Длительность этого режима в периодах импульса высокой частоты равна величине усредненного фазового рассогласования за цикл накопления.

Сигнал такой длительности с выхода счетчика на вычитание 5 поступает на вход делителя 2, переводит делитель 2 в режим "управляем ое деление".

Сигнал с выхода (k +1п+ 4 ) -го разряда сумматора 4 поступает на управляющий вход 8 делителя 2 и определяет вид "управляем orо деления".

Сигнал с выхода счетчика на вычитание

5 одновременно поступает на вход выделителя фронтов 3, с выхода которого сигнал поступает на вход "обнуление" 10 сумматора 4 и производит "обнуление" т. е. установку сумматора 4 в исходное состояние для следующего цикла накопления. Фаза выходного сигнала, снимаемого с выхода

К-го разряда делителя 2 с точностью до одного импульса высокой частоты осуществляет слежение за усредненной фазой значащих моментов входного сигнала данных.

Усреднение фазы в течение достаточно длительного цикла накопления дает фазу математического ожидания . значащего момента, слежение эа усредненной фазой дает снижение динамической погрешности фазирования и, соответственно, повышение исправляющей способности устройства фазирования.

Формула изобретения

Устройство для синхронизации двоичных сигнал ов, с о держащее за дающий гене ра тор, выход которого подключен к одному из входов делителя, и к другому входу которого подключен вход выделителя фронтов сигнала, о т л и ч а ю щ е е с я тем, что, с целью повышения точности и быстродейс твия фазир ования, введены сумматор, сч етчик на вычитание, счетчик на сложение и дополнительный выделитель фронтов, при этом выходы "К разрядов делителя подключены к (k + N + 2 ) входам сумматора, выход последнего разряда которого подключен к управляющему входу делителя, а (k + 4 ) выходы — к соответствующим входам счетчика на вычитание, к управляющему входу которого подключен выход счетчика на сложение, а выход счетчика на вычитание через выделитель фронтов сигнала подключен к входу "Обнуление" сумматора, управляющий вход которого соединен со вхо544162

Составитель Е. Любимова

Редактор Ю. Комаров Техред M. Левицкая Корректор А, Лакида

Заказ 873/73 Тираж 815 Подписное

UHHHIIH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 дом счетчика на сложение и с выходом дополнительного выделителя фронтов сигнала.

Источники информации, принятые во внимание при экспертизе:

1. Мартынов Е. М. Синхронизация в 5 системах передачи данных дискретных сообщений, М., "Связь", 1972., стр. 130.

2. Авторское свидетельство СССР

%403096, М. Кл. Н 04 Ь 7/10, 1973 (прототип).