Арифметическое устройство

Иллюстрации

Показать всеРеферат

(11) 544964

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Gom Советских

Социалистических, Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 22.04.74 (21) 2020098;24 с присоединением заявки «¹ (23) Приоритет

Опубликовано 30.01.77. Бюллетень № 4

Дата опубликования описания 15.02.77 (51) М Кч G 06F 7 50

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.325(088.8) (72) Авторы изобретения

Н. М. Кязимов, А. Г. Алиев, Л. Т. Багдатьев и С. М. Вахабов (71) Заявитель Научно-исследовательский и проектный институт по комплексной автоматизации нефтяной и химической промышленности (54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

Изобретение относится к области автоматики и цифровой вычислительной техники и мо кет быть использовано прп реализации технических средств обработки информации и

ЗЦВМ.

Известно арфметическое устройство, построенное на базе двоичного сумматора (1), состоящего из повторяющихся п-разрядных узлов, каждый из которых включает и-разряднъ|и дв011чныи c)iмматор, узел переноса, узел инвертирования. Однако такое устройство невозмо кно использовать для работы с двопчнодесятичными кодами.

Известно тактке ар11фмет1!ческое устройство, наиоолее близкое по техническому решению к изобретению, содержащее в каждом

i-м разряде двоичный сумматор, входы которого соединены с информационными шинами и с выходом переноса из (i — 1)-го разряда, а выход — с входом элемента ИЛИ, узел инвертирования, выходы которого подключены к другим входам узла управления переносом и третьему входу двоичного сумматора, элементы И, ИЛИ (2).

Недостатком этого устройства является необходимость введения большого количества коммутирующих и сборочных элементов при использовании его в устройствах обработки данных, в которых числа могут поступать как в двоично-десятичном, так и в двоичном кодах, а также, если нужно обеспечить возможность инвертирования выходного кода.

Цель изобретения — упрощение устройства.

Это достигается тем, что в устройстве один из выходов узла управления переносом соединен с одним из входов элемента И, другой вход которого подключен к шине переноса пз (i — 1)-го разряда, а другой выход узла управления переносом — с одним из входов элеИ мента ИЛИ, другие входы которого подключены соответственно к выходу переноса двоичного c) мматор2, и выходу элемента И 11 к управляющей шине устройства, а выход 3;Icмента ИЛИ подсоединен к четвертому входу

15 двоичного сумматора.

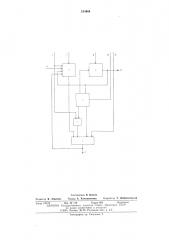

На чертеже приведена схема 1-го разряда устройства.

Устройство содержит двоичный сумматор 1, узел 2 инвертирования, узел 3 управления пе20 реносом, элемент И 4, элемент ИЛИ 5. Вход

6 переноса (i — 1)-ro разряда соединен с первым входом двоичного сумматора 1 и первым входом элемента И 4, управляющие входы 7, 8 и 9, 10 устройства — соответственно с уп25 равляющими входами двоичного сумматора 1, узла 2 инвертирования и узла 3 управления переносом и элемента ИЛИ 5. Информационные шины 11 соединены с вторым входом сумматора 1, входная шина сумматора — с вы30 ходом узла 2 инвертирования и с первым вхо544964

) 10

20

Зо

3 дом узла 3 управления переносом. Выход узла инвертирования подключен к выходным информационным шинам 12 и второму входу узла управления переносом, первый выход узла управления переносом — к второму входу. элемента 11, к четырем входам элемента ИЛИ 5 присоединены соответственно выход переполнения сумматора 1, выход элемента И, второй выход узла управления переносом и управляющий вход 10.

Работает устройство следующим образом.

При двухтактной системе синхронизирующих сигналов на управляющий вход 8 подается либо признак прямого кода (при сложении), либо инверсного (при вычитании), на управляющий вход 9 — признак рея има, задающий основание q системы счисления, в которой должно работать устройство. При числе разрядов сумматора 1, равном п, максимальное возмо к ое значение Я основания системы счисления q рашю 2".

На первом такте в сумматоре 1 выполняется сложение или вычитание чисел Z,, содержащегося в сумматоре, и Х,, поступающего на вход 11. В результате в сумматоре образуется при сложении число Z ;= IZ;+X;I Q, а при вычитании Z ;= jZ;+(Q — Х,) Q.

После первого такта на первом выходе узла управления переносом формпру.ется признак

«порогового» кода, который равен при сложении числу (q — 1), а прп вычитании — нулю.

Если q Q, то на втором выходе узла управления переносом формируется признак некомплектного кода, который возникает когда, q

Признак переноса на выходе сумматора 1 соответствует «переполнению» сумматора, т. е. случаям: при сложении Z;+X;) Q — 1, прп вычитании 2,— Хг(0.

Таким образом после первого такта на выходе элемента ИЛИ 5 возникает признак переноса в одном из трех следующих случаев: сумматор 1 переполнен, одновременно присутствуют признак переноса предыдущего разряда на входе 6 и признак «порогового» кода, присутствует признак некомплектного кода.

На втором такте к числу Z; добавляется (плп вычитается) число 1, если есть сигнал на входе 6, число (Q — q), при сигнале на выходе 13 и число (Q — q+1), когда присутствуют оба сигнала.

После двух тактов работы на выходах сумматоров всех разрядов цифры представлены при положительном результате в прямом коде, при отрицательном — в коде дополнения до q — 1.

Выдача результата из сумматора может производиться как в прямом, так и в инверсном коде. Для выдачи положительных чисел на вход 8 устройства подается соответствующий управляющий сигнал (признак либо прямого, либо инверсного кода). Для выдачи отрицательных чисел предварительно поступает управляющий сигнал на вход 10 и в сумматоре выполняется сложение по четвертому входу, в результате чего к содержимому сумматора 1 прибавляется число (Q — q). Затем происходит выдача. При этом для выдачи прямого кода на вход 8 необходимо подать признак инверсного кода и наоборот.

Сложность предложенного устройства и прототипа оценивается числом базовых элементов при Q=16 и q — 10 для предложенного решения составляет 14,5, а для прототипа—

20. Таким образом, предложенное решение позволяет сократить расход элементов на

27,5%.

Формула изобретения

Арифметическое устройство, содержащее в каждом -м разряде двоичный сумматор, входы которого соединены с информационными шинами и с выходом переноса из (i — 1) -го разряда, а выход — с входом элемента ИЛИ, узел инвертирования, выходы которого соединены с другими входами узла управления переносом и третьим входом двоичного сумматора, элементы И, ИЛИ, отличающееся тем, что, с целью упрощения устройства, в нем один из выходов узла управления переносом соединен с одним из входов элемента

И, другой вход которого подключен к шине переноса из (i — 1)-го разряда, а другой выход узла управления переносом соединен с одним пз входов элемента ИЛИ, другие входы которого подключены соответственно к выходу переноса двоичного сумматора, к выходу элемента 11 и к управляющей шине устройства, а выход элемента ИЛИ соединен с четвертым входом двоичного сумматора.

11c î÷íèêè информации, принятые во внимание прп экспертизе:

1. Китов А, И. и Крш пцкпй Н. А. Электронные цифровые машины и программирование.

М., 1959, с. 159 — 164.

2. Аит. св. Л 441562, G 061 7/385, 1972.

544964

Составитель В. Белкин

Редактор В. Зенкевич Техред А. Камышникова Корректор T. Добровольская

Заказ 129/13 Изд. № 136 Тираж 899 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4;5

Типография, пр. Сапунова, 2