Ячейка памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОЬРЕтЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ппц 545007

Cits Свветекик

Социалистических.

Республик (б1) Дополнительное к авт. свид-ву (22) Заявлено 28.11.73 (21) 1973699/24 с присоединением заявки № (23) Приоритет

Опубликовано 30.01.77. Бюллетень № 4

Дата опубликования описания 23.02.77 (51) М. Кл. - G 11С 11, 40

Государственный комитет

Совета Министров СССР по делам изабретеиий и открытий (53) УДК 681.327.66 (088.8) (72) Авторы

Л. П. Домнин, Л. H. Петров, И. H. Тонких и Д. П. Федоров изобретения (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ

Изобретение относится к области вычислительной техники и применимо в быстродействующих опер ативных запоминающих устройствах с малой потребляемой мощностью, при изготовлении больших интегральных схем ЗУ с высокой степенью интеграции, а также в системах автоматики, телемеханики, радиоизмерительной технике, Известна ячейка памяти, представляющая собой триггер с двумя входными и двумя выходными вентилями, содержащий усилительные транзисторы, базы которых подключены через переходы эмиттер — база эмиттерных повторителей к пассивным резисторным нагрузкам противоположных плеч ячейки, а э"ièòòåðû соединены между собой и подключены к коллекторам транзисторов переключателей тока (1).

Недостатками ячейки являются ее относительная сложность построения (10 транзисторов и б резисторов) и значительная потребляемая мощность, что затрудняет ее применение в БИС ЗУ с высокой степенью интеграции.

Изве=тна также ячейка памяти, наиболее близкая по технической сущности к изобретению, содержащая многоэмиттерные транзисторы, коллекторы которых подключены к Bbiкодлой шине, адресные шины, соединенные с первыми эмиттерами многоэмиттерных транзисторов, вторые эмиттеры которых подключсны к коллекторам нагрузочных транзисторов, а эмиттеры нагрузочных транзисторов — к шине постоянного напряжения, базы многоэмиттерных транзисторов подсоединены к коллекторам нагрузочных транзисторов (2).

Однако такая ячейка памяти имеет малое быстродействие и слабую помехоустойчивость.

При работе ячейки в широком диапазоне

1О температур с использованием высокостабильного источника питания коэффициенты усиления транзисторов меняются в значительной степени, вследствие этого состояние бистабильности ячейки рез" î изменяется, что и вы15 зывает потерю информации.

Поскольку активные компоненты ячейки работают с очень Màëыми статическими коэффициентами передачи, т. е. в режимах глубокого насыщения и отсечки, то, следовательно, 20 в режиме микротоков скорость срабатывания ячейки мала.

Наличие относительно высокого коэффициента связи между эмиттерами адресных транзисторов и транзисторов плеч ячейки при зна25 чительных токах эмиттеров адресных транзисторов приводит к ухудшению помехоустойчивости.

1\ель изобретения — повышение быстродействия и помехоустойчивости ячейки памяти.

ЗО Это достигается тем, что в ячейку введены

545007 диоды, аноды которых подключены к шине постоянного напряжения,,катоды диодов соединены с базами нагрузочных транзисторов и с третьими эмиттерами многоэмиттерных транзисторов.

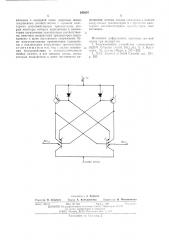

1-1а чертеже представлена схема предлагаемой ячеики памяти.

Ячейка памяти состоит из инверсно включенных многоэмпттерных (по три эмиттера) усилительных транзисторов 1 и 2 в каждом плече, коллекторы их соединены между собой что создает общую коллекторную связь и cIIOсобствует уменьшению размеров ячейки в интегральном исполнении.

11ервые эмиттеры транзисторов 1, 2 (считая сверху вниз по порядку) соответственно подключены к термокомпенсирующим диодам 3 и 4 и к базам нагрузочных транзисторов 5, 6 противоположного типа, проводимости, эмиттеры которых соединены между собой и с анодами диодов 3, 4 и подключены к источнику питания. Коллекторы транзисторов 5, б соединены соответственно с вторыми эмиттерами транзисторов 2, 1 и базами этих же транзисторов 1 и 2. Третьи эмиттеры транзисторов 1, 2 являются адресными, а коллекторы подсоединены к клемме выбора ячейки или опорной точке. Ячейка памяти строго симметрична.

В одном из состояний ячейки потенциал базы многоэмиттерного транзистора 2 выше, чем потенциал базы транзистора 1 относительно их общего коллектора. В этом случае образуется два кольца с замкнутой положительной термостабильной обратной связью. Первое кольцо состоит из соединенных между собой коллектора транзистора б и второго эмиттера транзистора 1 и катодом прямосмещенного диода 4 с базой и первым эмиттером транзистора 2, с базой транзистора б.

Второе кольцо, симметричное первому, состоит из соединенных между собой коллектора транзистора 5 и второго эмиттера транзистора 2 с базой транзистора 1 и первого эмитте ра транзистора 1 с базой транзистора 5 и катодом прямосмещенного диода 3.

При повышении потенциала базы транз.(стора 2 потенциалы эмиттеров этого же трачзистора понижаются, в результате повышается ток через диод 4, и следовательно, ток базы и коллектора транзистора б. Повышение тока коллектора транзистора б ведет к увеличению тока базы транзистора 2, т. е. еще к большему повышению потенциала базы транзистора 2. Весь процесс происходит в активном режиме до значений коэффициента усиления,по кольцу обратной связи, равного единице, Потенциал первого эмиттера транзистора 2 приближается к потенциалу его коллекра, а потенциал коллектора транзистора 6— к потенциалу его эмиттера, т. е. оба транзистора находятся на границе критического режима.

Поскольку база многоэмиттерного транзистора 2 общая, то второй эмиттер этого транзистора также стремится к потенциалу кола

)()

ЗО

60 лектора. В этом случае потенциал базы транзистора 1 понижается до потенциала его коллектора и транзистор закрывается. Это приводит к понижению тока через прямосмещенный диод 3, что соответственно снижает ток базы грапзнстора 5 и ток его коллектора, а значит и ток второго эмиттера транзистора 2, Благодаря наличию кольца положительной обратной связи процесс происходит в активном режиме до значения коэффициента усиления, равного единице. При этом ток транзисторов

1 и 5 резко уменьшается и транзисторы находятся на границе режима отсечки. Поскольку ток второго эмиттера транзистора 2 резко снижен, а ток базы приближается к величине тока коллектора транзистора б, то транзистор 2 по второму эмиттеру входит в режим н а сы щен ия.

Транзистор 1 входит в режим отсечки по второму эмиттеру, и этот режим становится еще более устойчивым за счет взаимовлияния обратной связи и состояния отсечки. Состояние бистабильности ячейки значительно повышается. Поэтому весьма значительные токи адресных выходов (Вых.(, Вых.2) не ухудшают помехоустойчивости в работе ячейки. По той же причине ячейка более помехоустойчива прп изменениях напряжений источников питания.

В рабочем состоянии ячейки потребление тока происходит,по цепям: транзистор 6 — 03за транзистора 2 и диод 4, переход эмиттерколлектор транзистора 2. Другое плечо находится в состоянии, близком к отсечке, и потребления тока почти нет, т. е. при работе ячейки ток потребляется одним плечом, что снижает мощность ее потребления.

Диоды 3, 4 являются не только элементами нагрузки в кольце обратной связи, но и выполняют функции термостабилизации базовых токов транзисторов 5, б, что улучшает термостабильность ячейки при работе в широком диапазоне температур, Поскольку транзисторы 5, служат активными динамическими нагрузками транзисторов 1, 2, т. е. сами выполняют функции усиления поступающего сигнала и соответствепIIo транзисторы 2 и 1 являются нагрузочными элементами транзисторов 5, б, то процесс нарастания фронта иi(пульса происходит с высокой скоростью, так как время фронта обратно пропорционально произведению усиления на полосу частот при максимальном коэффициенте усиления, т. е. определяется коэффициентом усиления и частотными свойствами компонентов.

Ячейка памяти устойчиво работает при температуре от — 60 до +125 С, время выборки

5 — 15 мксек, допустимая нестабильность источника питания +30,(о, Средняя потребляемая мощность — не более 1 мквт.

Формула изобретения

Ячейка памяти, содержащая многоэмиттерные транзисторы, коллекторы которых под545007

Составитель Л. Воронин

Техрсд А. Камышникова Коррек;ор И. Позняковская

Рсдактор В. Зенкевич

Заказ 130/17 Изд. ¹ 163 Тираж,69 11 кс:попсе

Ц1-1ИИПИ Государстве1нгого комитета Сонета Мини тров СССP но делам изооретсний и открьппп

113035, Москва, К-3;>, Рамн1ская нас, д 4, 5

Типография, пр. Сануноьа, и ключены к выходной шине, адресные шины, соединенные соответственно с .. ервыми эмиттерами многоэмиттерных транзисторов, вторые эмиттеры которых подключены к коллекторам нагрузочных транзисторов соответственно, эмиттеры нагрузочных транзисторов подсоединены к шине постоянного напряхкения, базы многоэмиттерных транзисторов подключены к коллекторам нагрузочных транзисторов, отличающаяся тем, что, с целью повышения быстродействия и помехоустой 1пвости ячейки памяти, в нее введены д:1оды, аноды которых подключены к шине постоянного напряжения, катоды диодов соединены с оазамп нагрузо гнвгх транзисторов и с трст1:I .ìii эмиттсрам:1 многоэмпттерных тр;1 1з11 горoi сооТвественно.

Источники информ ац11п, прпнятыс во внимание iipII эк перт:1зе:

1. Запомина1ощпс уст1зойства совремс1шых

ЗЦВМ. Сбор пп стате11. Под ред. А. Л. Кру.i=кого. Ч., пзд-во «, !пр», с. 277 — 302.

2, Л.I:. do гпаl 01 Solid Cii cIIits, oci. 191 р, 283.