Фазовый дискриминатор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

«>546087

Союз Советских

Соцннлнстнческнн

Республик (bl) Дополнительное к авт. свид-ву— (22) Заявлено 17.11.75 (21) 2190782/21 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 05.02.77. Бюллетень № 5 (45) Дата опубликования описания 28.03.77 (51) М.Кл.2 Н 03 D 13/00

Государственный комитет

Совета Мнннстров СССР по делам изобретений (53) УДК 621.374.32 (088.8) н открытий (72) Авторы изобретения

А. Я. Котовщиков, В. Г. Латюк и Э. Г. Могелевский (71) Заявитель (54) ФАЗОВЫ Й Д ИСКР ИМ И H ATOP

Изобретение относится к импульсной технике.

Известен фазовый дискриминатор, содержащий два канала, в каждом из которых включены счетчик, триггер и логический элемент И, оба канала подключены к входам цифрового счетчика импульсов, и блок индикации знака разности (1). Известный дискриминатор имеет сложную схему.

Наиболее близким техническим решением к данному изобретению является фазовый дискриминатор, содержащий триггер, выходы которого соединены с первыми входами логических элементов И, вторые входы которых соединены с входами триггера и через формирователи с источниками сравниваемых сигналов (2).

Однако такой дискриминатор недостаточно устойчив в работе.

Целью изобретения является повышение устойчивости работы дискриминатора путем ограничения диапазона измерения фазового рассогласования сигналов.

Достигается это тем, что в фазовый дискриминатор введены два дополнительных логических элемента И, два логических элемента И вЂ” НЕ и два дополнительных триггера, причем первые входы дополнительных логических элементов И соединены с выходами основных логических элементов И и первыми входами дополнительных триггеров, вторые их входы соединены с первыми выходами соответствующих дополнительных триггеров и одними входами логических элементов И вЂ” НЕ, 5 второй вход одного из которых соединен с выходом основного триггера, а второй вход другого — с выходом первого логического элемента И вЂ” НЕ, при этом выходы дополнительных логических элементов И подключены к

10 вторым входам дополнительных триггеров.

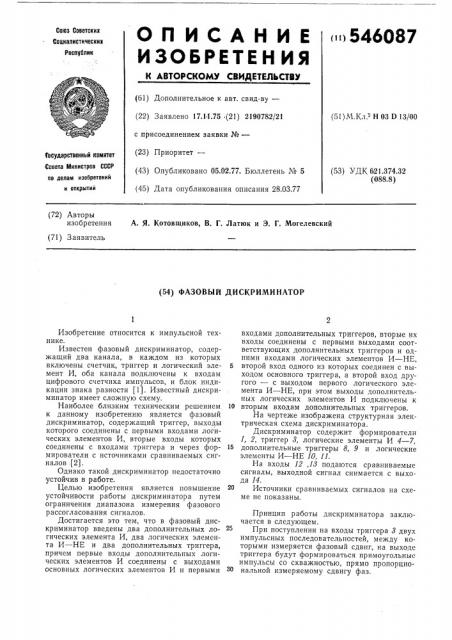

На чертеже изображена структурная электрическая схема дискриминатора.

Дискриминатор содержит формирователи

1, 2, триггер 8, логические элементы И 4 — 7, 15 дополнительные триггеры 8, 9 и логические элементы И вЂ” НЕ 10, 11.

На входы 12,И подаются сравниваемые сигналы, выходной сигнал снимается с выхода 14.

Источники сравниваемых сигналов на схеме не показаны.

Принцип работы дискриминатора заключается в следующем.

При поступлении на входы триггера 8 двух импульсных последовательностей, между которыми измеряется фазовый сдвиг, на выходе триггера будут формироваться прямоугольные импульсы со скважностью, прямо пропорциоЗо нальной измеряемому сдвигу фаз.

546087

lO

Если существует разность частот входных импульсных последовательностей, то при достижении фазовым сдвигом граничного значения линейного диапазона измерения триггера 8 на выходе последнего происходит нарушение монотонности изменения сигнала, среднее значение которого из-за этого нарушения имеет вид пилообразной кривой. В этот же момент на выходе одного из элементов 4 или 5, на вход которого поступает импульсная последовательность большей частоты, формируется импульс, который через элемент б или 7 поступает на первый вход соответствующего дополнительного триггера 8 или 9. В исходном состоянии эти триггеры устанавливаются в такое положение, при котором выходной сигнал триггера 3 беспрепятственно проходит через элементы 10 и 11. В момент формирования импульса на выходе элементов 4 или 5 соответствующий триггер 8 или 9 устанавливается в положение, обеспечивающее запрет прохождения выходного сигнала измерителя через элементы 10 и 11. Если запрет поступает на элемент 10, то на выходе устройства устанавливается напряжение, соответствующее нижней границе насыщения, а при поступлении запрета на элемент 11 напряжение на выходе устройства будет соответствовать верхней границе насыщения.

Запоминание выходного сигнала, соответствующего той или иной границе насыщения, будет обеспечиваться до тех пор, пока знак разности частот входных сигналов остается неизменным. Если же в процессе работы происходит изменение знака разности частот входных сигналов, то при достижении фазовым сдвигом границы диапазона линейного измерения триггера 8 уже на выходе другого элемента 5 или 4 будет формироваться импульс, который в зависимости от состояния обеспечит установку триггера 8 в исходное положение или в положение насыщения, соответствующее другой границе линейного диапазона измерения. Если ранее триггер 8 находился в состоянии, обеспечивающем запрет на входе элемента 11, а импульс, соответствующий границе линейного измерения, формировался на выходе элемента 5, то прохождение этого импульса на первый вход триггера

9 оказывается невозможным из-за наличия запрета на входе элемента 7 от триггера 8.

В этом случае импульс с выхода элемента 5 проходит только на второй вход триггера 8; что обеспечивает установку триггера 3 в исходное состояние, при котором снимается запрет с логических элементов 7 и 11. Следующее формирование импульса на выходе элемента 5 приводит к срабатыванию триггера

9 и соответственно к установке запрета на элементах б и 10. Последнее приведет к установке на выходе устройства напряжения, соответствующего нижней границе насыщения.

Формула изобретения

Фазовый дискриминатор, содержащий триггер, выходы которого соединены с первыми входами логических элементов И, вторые входы которых соединены с входами триггера и через формирователи с источниками сравниваемых сигналов, отличающийся тем, что, с целью повышения устойчивости работы дискриминатора, в него введены два дополнительных логических элемента И, два логических элемента И вЂ” НЕ и два дополнительных триггера, причем первые входы дополнительных логических элементов И соединены выходами основных логических элементов И и первыми входами дополнительных триггеров, вторые их входы соединены с первыми выходами соответствующих дополнительных триггеров и одними входами логических элементов И вЂ” НЕ, второй вход одного из которых соединен с выходом основного триггера, а второй вход другого — с выходом упомянутого первого логического элемента И вЂ” HE, при этом выходы дополнительных логических элементов И подключены к вторым входам дополнительных триггеров.

Источники информации, принятые во внимание при экспертизе данной заявки:

1. Патент США № 3808407, кл. 235-92 F О, 30.04. 74.

2. Патент Великобритании № 1283801, кл.

Н 3 А, 26.08.73.

546087

Составитель А. Артюх

Техред В. Рыбакова

Корректор В. Гутман

Редактор Н. Петрова

Тип. Харьк. фил. пред. «Патент»

Заказ 114/296 Изд. Хд 426 Тираж 1054 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )К-35, Раушская наб., д. 4/5