Устройство для умножения

Иллюстрации

Показать всеРеферат

ийтбнтнс

ОП ИСАН

ИЗОБРЕТЕН 546883

Coca Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕ (61) Дополнительное к авт. свид(22) Заявлено 03.04.74 (21) 201178 с присоединением заявки №

) М. Кл 2 G 06F 7/48 (23) Пр ор

Приоритет

Совета Министров СССР по делам изобретений и открытий

Опубликовано 15.02.77. Бюллетень

Дата опубликования описания 13.

) УДК 687.325(088.8) (72) Авторы изобретения

A. Ф. Комиссаров и Ю. А. Яковлев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при проектировании арифметических устройств вычислительных машин.

Известны устройства умножения матричного типа (1). Недостатком этих устройств являются большие затраты оборудования. Например, для умножения «т»-разрядного «S»ичного числа на одноразрядное необходимо

«m» одноразрядных «S»-ичных матриц умножения.

Наиболее близким техническим решением к данному изобретению является устройство, содержащее сумматор, элементы ИЛИ, элементы И, причем входы сумматора подключены к выходам соответствующих элементов

ИЛИ, входы каждого из которых подключены к выходам соответствующих элементов

И, первые входы которых подключены к соответствующим шинам множимого (2).

Недостатками такого устройства являются большие затраты оборудования на матрицу и малое быстродействие, обусловленное задержкой сигнала на время срабатывания схем совпадения матрицы.

С целью повышения быстродействия и надежности предлагаемое устройство содержит шифратор, входы которого подключены к соответствующим шинам множителя, а выходы шифратора подключены ко вторым входам соответствующих элементов И.

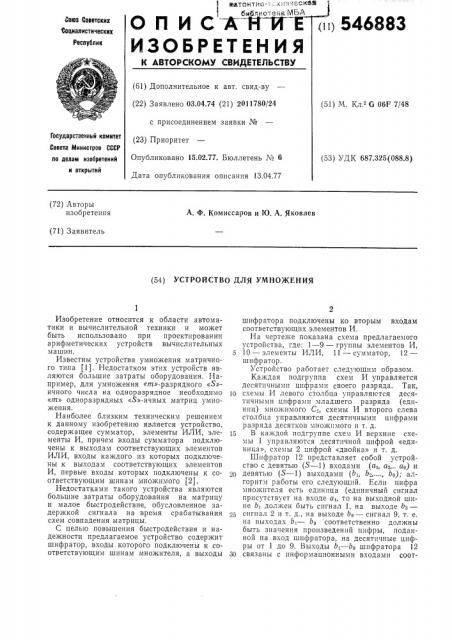

На чертеже показана схема предлагаемого устройства, где: 1 — 9 — группы элементов И, 5 10 — элементы ИЛИ, 11 — сумматор, 12— шифратор.

Устройство работает следующим образом.

Каждая подгруппа схем И управляется десятичными цифрами своего разряда. Так, 1р схемы И левого столбца управляются десятичными цифрами младшего разряда (единиц) множпмого С;, схемы И второго слева столбца управляются десятичными цифрами разряда десятков множимого и т. д.

15 B каждой подгруппе схем И верхние схемы 1 управляются десятичной цифрой «единица», схемы 2 цифрой «двойка» и т. д.

Шифратор 12 представляет собой устройство с девятью (S — 1) входами (a„a, аД и

2р девятью (S — 1) выходами (b, b> ", bg); алгоритм работы его следующий. Если цифра множителя есть единица (единичный сигнал присутствует на входе аь то на выходной шине b должен быть сигнал 1, на выходе bz,— сигнал 2 и т. д., на выходе bg — сигнал 9, т. е. на выходах b> — bg соответственно должны быть значения произведений цифры, поданной на вход шифратора, на десятичные цифры от 1 до 9. Выходы b< — Ье шифратора 12

30 связаны с информационными входами соот546883

Формула изобретения

Составитель В. Жуков

Редактор Н. Каменская Техред Е. Хмелева Корректор Л. Котова

Заказ 1123/13 Изд. № 177 Тираж 899 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ветствующих схем И, выход b> соединен с информационными входами схем И 1, выход

Ьз — с информационными входами схем И 2 и т, д.

Выходы подгрупп схем И связаны со входами соответствующей 1-той схемы ИЛИ 10 (1

Пусть множимое будет представлено числом 0...019, а множитель — 9. Тогда на выходе шифратора b< будем иметь число 9, на выходе Ьз — 18, и т. д. и на выходе ов — 81.

Цифрой множимого C -> будет открыта схема И 9, нижняя в левой подгруппе схем И, и на вход схемы ИЛИ 10 (крайняя слева) пройдет число с шины Ьз 81. Последнее с выхода схемы ИЛИ поступит на вход сумматора 11. Цифрой множимого Са-1 будет открыта схема И 1 (вторая слева в верхнем ряду) и число с шины bi 9 пройдет через схему И на вход соответствующей схемы ИЛИ и далее на сумматор 11. В сумматоре 11 производится сложение полученных выше чисел с соответствующим сдвигом. Так в нашем примере 81+90= 171.

Предложенное устройство выгодно отличается от прототипа. Затраты оборудования уменьшены за счет исключения схем ИЛИ одноименных цифр множимого и за счет замены матрицы шифратором (при замене матрицы шифратором исключаются 81 схема И и значительное число связей). Надежность предлагаемого устройства выше чем у прототипа, за счет уменьшения числа элементов и

5 связей.

Устройство для умножения, содержащее

10 сумматор, элементы ИЛИ, элементы И, причем входы сумматора подключены к выходам соответствующих элементов ИЛИ, входы каждого из которых подключены к выходам соответствующих элементов И, первые

15 входы которых подключены к соответствуюющим шинам множимого, о т л и ч а ю щ е ес я тем, что, с целью повышения быстродействия и надежности устройства, оно содержит шифратор, выходы которого подключены к соответствующим шинам множителя, а выходы шифратора подключены к вторым входам соответствующих элементов И.

Источники информации, принятые во внимание при экспертизе:

1. И. В. Прангишвили и др. «Микроэлектроника и однородные структуры для построения логических и вычислительных устройств». М., «Наука», 1967.

2. Авторское свидетельство СССР№392497, 30 М. кл.а С 06F 7/52, 1971.