Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАН И Е

ИЗОБ Ет ЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ii) 546933

Союз Советских

Социалистических

Республик (б1) Дополнительное к авт. свид-ву (22) Заявлено 20.03,75 (21) 2115123/24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 15.02.77. Бюллетень № 6

Дата опубликования описания 17.03.77 (51) Ч, Кл.- "G 11С 11/00

Государственный комитет

Совета Министров СССР (53) УДК 681.327.66 (088.8) по делам изобретений н открытий (72) Авторы изобретения (71) Заявитель

С. H Аврамова, А. В. Городний, В. И. Корнейчук и В. И. Гусак

Киевский ордена Ленина политехнический институт им. 50-летия

Великой Октябрьской социалистической революции (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и предназначено для построения запоминающего устройства (ЗУ) повышенной надежности.

Известно запоминающее устройство, в котором слова накапливаются в группы сдвигающих матриц и каждая группа накапливает один бит одного слова (1).

Однако в указанном запоминающем устройстве отсутствуют цепи управления коммутацией регистра адреса с накопителем.

Наиболее близким по технической сущности к данному изобретению является запоминающее устройство, содержащее регистр слова, один из входов которого подключен к первым выходам адресного блока, второй выход адресного блока соединен со входом генератора синхроимпульсов, вход адресного блока соединен с первым выходом блока управления, второй выход которого соединен с первыми управляющими входами коммутаторов, накопитель, выходы которого подключены к информационным входам первого коммутатора (2).

Однако в указанном запоминающем устройстве не предусмотрены, во-первых, контроль информации в накопителе, во-вторых, возможность какого-либо исправления появившихся искаженных разрядов, и в третьих, не предусмотрена возможность пересылки информации с отказавшего регистра на исправный при повторяющ1гхся ошибках в разряда« накопителя.

Целью изобретения является повышение информационной надежности запоминающего устройства.

Указанная цель достигается тем, что в запоминающее устройство введены блок регистрации отказов, блок декодирования, блок за10 дания номера заменяющей ячейки памяти накопителя, элементы И, ИЛИ, блок кодирования, входы которого через регистр слова подключены к выходам элементов ИЛИ, вы«оды блока кодирования соединены со в«одамп

15 второго коммутатора, вы«оды которого подключены к первым входам элементов И, вторые в«оды элементов И подключены к выходу генератора син«роимпульсов, вы«оды элементов И соединены со в«одами накопителя, вы20 «оды первого коммутатора подключены к информационным входам блока декодирования, управляющий в«од которого соединен со вторым выходом блока управления, с управляющим входом блока регистрации отказов, управляющим входом блока задания номера заменяющей ячейки памяти накопителя, управляющим входом блока кодирования, первый выход блока декодирования соединен с одним из входов элементов ИЛИ, другие входы коЗ0 торых подключены к информационным шинам

546933

2О

25 зо

G5 устройства, второй выход блока декодирования соединен со входом блока регистрации отказов, выход которого подключен ко входу блока задания номера заменяющей ячейки памяти накопителя, выходы которого соединены со вторыми управляющими входами коммутаторов.

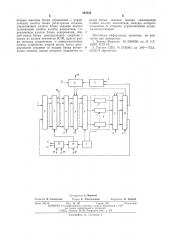

На чертеже показана функциональная схема предлагаемого устройства.

Оно содержит информационные шины 1, подключенные к одним входам элементов

ИЛИ 2, выходы которых подключены к информационным входам регистра слова 3, а выходы последнего к информационным входам блока кодирования 4, выходы которого подключены к Одним из входов коммутатора

5. Его выходы подключены к первым входам элементов И 6, вторые входы которых подключены к выходу генератора синхроимпульсов 7. Выходы элементов И 6 связаны с информационными входами накопителя 8, содержащего и сдвиговых регистров ячеек, управляющие входы которых подключены к выходу генератора синхроимпульсов 7.

Выходы накопителя 8 подсоединены к одним из входов коммутатора 9, à его выходы подключены к информационным входам блока декодирования 1Î, первые выходы которого связаны со вторыми входами элементов

ИЛИ 2. Вторые выходы блока декодирования

10 подсоединены ко входам блока регистрации отказов 11, а третьи выходы — к другим входам коммутаторов 5 и 9. Выходы алака регистрации отказов 11 соединены с одними входами блока задания номера заменяющей ячейки памяти 12 накопителя, выходы котороГО подключены к управляlощим входам коммутаторов 5 и 9. 11ервый выход блока управления 13 связан с соответствующим входом адресного блока 14, а вторые выходы блока управления 13 связаны с управляющими входами блока кодирования 4, коммутаторов 5, 9, блока декодирования 10, блока регистрации отказов 11, блока задания номера заменяющей ячейки памяти 12. Блок управления

13 имеет также входы 15, 16 (начало операции и код операции соответственно) и выход

17 (конец операции).

Второй вход адресного блока 14 связан с адресными шинами 18 устройства, а третий вход с выходом генератора синхроимпульсов 7. Выход адресного блока 14 подключен к управляющему входу регистра слова 3, выходы которого подключены также к выходным информационным шинам 19 устройства.

Информационное слово поступает на входы

1 и через элементы ИЛИ 2 записывается в ре-гистр слова 3, а с выходов последнего поступает на блок кодирования 4 плп на выходы

19. В блоке кодирования 4 в соответствии с информационными разрядами происходит образование контрольных разрядов. "1ерез коммутатор 5 и элементы И 6 слово поступает на сдвиговые регистры накопителя 8. Импульсы, поступившие от генератора синхроимпульсов

7 ?Ia сдвигающие пепи регистров накопителя

8, осуществляют синфазный и синхроннь?й сдв??г информации.

Содержание каждого сдвигового регистра соответствует одному разряду всех слов, т. е. происходит параллельная запись, сдвиг и считывание слов. С выходов регистров через комм TBTop 9 c;10BG поступает на блок декодирования 10, а потам перезаппсывается в регистр слова 3. В блоке регистраь;пи отказов 11 фикс??РУется числО 06?IBP? 1?(c?IHblx ollll?60K в каждом регистре и достижение определенного, наперед заданного числ"., свидетельствует о появлении отказа в регистре. При этом происходит замена этого же регистра при помощи блока задания номера заменяющей ячейки памяти 12. Принцип замены состоит в том, что прп отказе i-ro регистра накопителя 8, информация пересылается в самый младший исправно работающий регистр, а его информация автоматически стирается. Коммутаторы 5 и 9 подключают блок кодирования 4 и блок декодирования 10 только к исправно работающим регистрам накопителя 8. Блок управления синхронизирует раба гу всего устройства.

Таким образом, описываемое запоминающее устройство выполняет те же функции, что и известное, но является более надежным в 10 — 10 раз при незначительных дополнительных аппаратурных затратах, что приводит к повышению его технико-экономической эффективности по сравнению с прототипом во столько же раз.

Формула изобретения

Запоминающее устройство, содержащее регистр слова, один из входов которого подключен к первым выходам адресного блока, второй выход адресного блока соединен со входом генератора синхроимпульсов, вход ацресного блока соединен с первым выходом блока управления, второй выход которого соединен с первыми управляющими входами коммутаторов, накопитель, выходы которого подклю?ены к информационным входам первого коммутатора, о тл ич а ющееся тем, что, с целью повышения информационной надежности устройства, в него введены блок регистрации отказов, блок декодирования, блок задания номера заменяющей ячейки памяти накопителя, элементы И, ИЛИ, блок кодирования, входы которого через регистр слова подключены к выходам элементов ИЛИ, выходы блока кодирования соединены со входами второго коммутатора, выходы которого подключены к первым входам элементов И, вторые входы элементов И подсоединены к выходу генератора спнхроимпульсов, выходы элементов И соединены со входами накопителя, выходы первого коммутатора подключены к информационным входам блока декодирования, управляющий вход которого соединен со

546933

Составитель А. Воронин

Текред Е. Жаворонкова

Редактор Н. Каменская

Корректор О. Тюрина

3a к а з 330, 13 Изд. ¹ 187 Тираж 769 Подписное

ЦНИИПИ Государственного комитета Совста Министров СССР по делам изобретений и открытий

113035, Москва, )K-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 вторым выходом блока управления, с управляющим входом блока регистрации отказов, управляющим входом блока задания номера заменяющей ячейки памяти накопителя, управляющим входом блока кодирования, первый выход блока декодирования соединен с одним из входов элементов ИЛИ, другие входы которых подключены к информационным шинам устройства, второй выход блока декодирования соединен со входом блока регистрации отказов, выход которого подключен ко входу блока задания номера заменяющей ячейки памяти накопителя, выходы которого соединены со вторыми управляющими входами коммутаторов.

Источники информации, принятые во внимание прп экспертизе:

1. Заявка Франции № 2206559, кл. G 11С

19/00, 12.07.74.

10 2. Патент СШЛ ¹ 3735361, кл. 340 — 172,5, 22.05.73 (прототип) .