Арифметическое устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАН ИЕ

ИЗОБРЕТЕН ИЯ

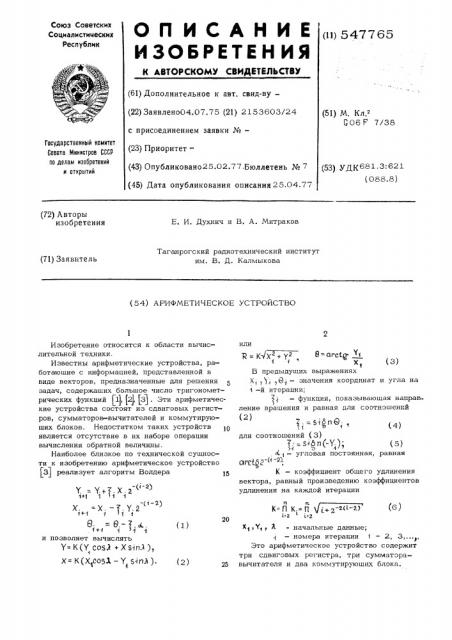

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено04.07.75 (21) 2153603/24 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 25.02.77.Бюллетень № 7 (45) Дата опубликования описания 25.04.77 (11) 547765 (S1) И. Кл.

406 Р 7/38

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий

РЗ) УД (681.3:621 (088.8) (72) Авторы изобретения

Е. И. Духнич и В. А. Митраков

Таганрогский радиотехнический институт им. В. Д. Калмыкова (71) Заявитель (54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники.

Известны арифметические устройства, работающие с информацией, представленной в виде векторов, предназначенные для решения задач, содержаших большое число тригонометрических функций (1), (2), )3) . Эти арифметические устройства состоят из сдвиговых регистров, сумматоров-вычитателей и коммутирующих блоков. Недостатком таких устройств является отсутствие в их наборе операции вычисления обратной величины.

Наиболее близкое по технической сушности к изобретению арифметическое устройство

3) реализует алгоритм Волдера

15 (6) 20 (2) Y. = Y+$ Х-2 х.„= Х. — (. Y. z "

8- = 8.— (.. .

1+1 и позволяет вычислять

Y= K(Y cos3 + Х зюЛ ), Х = К(Х сова — YÄ s np ). или

R = к4х, У 9= i«Q "i (3)

B предыдуших выражениях

X Y 8 — значения координат и угла на

1 -й итерации, 1 — функция, показываюшая направление врашения и равная для соотношений (2) .=ь еоб;, (4) для соотношений (3} (= " n(-Y); (5)

4. — угловая постоянная, равная ГС® 2).

К вЂ” коэффициент общего удлинения вектора, равный произведению коэффициентов удлинения на каждой итерации

- начальные данные; — номера итерации 1 = 2, 3,....

Это арифметическое устройство содержит три сдвиговых регистра, три сумматоравычитателя и два коммутируюших блока.

547765

Выходы всех разрядов первого и второго сдвиговых регистров соединены с соответствующими входами соответственно первого и второго коммутирующих блоков, управляющие входы которых подключены к первому входу устройства, выходы младших разрядов каждого из сдвиговых регистров — с первыми входами соответствующих сумматороввычитателей, выходы которых являются выходами устройства и подключены к входам старших разрядов тех же сдвиговых регистров. Выход первого коммутирующего блока подключен к второму входу второго сумматора-вычитателя, второй вход третьего сумматора-вычитателя соединен с вторым входом устройства, управляющие входы сумматоров-вычитателей — с третьим входом устройства.

Однако структура такого устройства не приспособлена для вычисления обратной вели- чины, которая часто встречается при решении тригонометрических задач.

Цель изобретения — расширение функциональных возможностей операции вычисления обратной величины.

Это достигается тем, что в арифметическое устройство дополнительно введен элемент

И, первый вход которого соединен с выходом второго коммутирующего блока, второй входс четвертым входом устройства, а выход— с вторым входом первого сумматора-вычитателя.

На чертеже показана структурная схема арифметического устройства, где 1, 2, 3— сдвиговые регистры; 4, 5 — коммутирующие блоки; 6, 7, 8 — сумматоры-вычитатели;

9 — выход Х; 1 0 — выход ; 1 1 — выход

g и „; 12 —; 13 — вход запрета; 14 —; 15 — вход,, 1 6 — вход коммутации.

Арифметическое устройство содержит три сдвиговых регистра, три сумматора-вычитат ля, два коммутирующих блока и элемент И.

Выходы регистра 1 подключены к соответствующим входам коммутирующего блока 4, выход блока 4 — к первому входу сумматора-вычитателя 6. Второй вход сумматора-вы-. читателя 6 соединен с выходом младшего разряда регистра 2, а выход — с входом того же регистра и выходом 10 устройства. Выхо- 50 ды регистра 2 связаны с соответствующими входами коммутирующего блока 5, выход блока 5 — с первым входом элемента И 12, второй вход которого является входом 13 с устройства, Первый вход сумматора-выччтателя 7 соединен с выходом элемента И

12, второй вход — с выходом регистра 1, а выход — с входом того же регистра и выходом 9 устройства. Выход регистра 3 подключен к первому входу сумматора-вычи60 тателя 8, второй вход этого сумматоравычитателя — к входу 14 устройства. Вход регистра 3 является выходом 11 устройства и подключен к выходу сумматора-вычитателя 8. Управляющие входы всех сумматороввычитателей соединены с входом 15 устройства, а управляющие входы коммутирующих блоков — с входом 1 6 устройства.

При решении соотношений (2) и (3) устройство работает по алгоритму (1), а при вычислении значения Z =.X в устройстве организуется интерационный процесс

-1

Х. = Х.+5.Õ 2 + 4 )4 О

Z =Z+7 Z 2 +4 1 о где Хо X (0,5

+4, )X„((3

-4, )X„l> 3, Z„ — значение обратной величины на

1 -й итерации (Z0 = 1 при Х)0 и 2,0

=- 1 прл X(0 ).

При вычислении соотношей (2) предлагае.-мое устройство работает следующим образом.

На вход 13 подается сигнал разрешения, значения Х4, Y и g„õðàíÿòcÿ соответственно в регистрах 1, 2, 3. С началом очередной итерации по- команде, поступающей на вход 16 из устройства управления, коммутирующие блоки 4, 5 соединяют соответствующие выходы регистров 1, 2 с входами сумматоров-вычитателей 6, 7 так, что на вход сумматора-вычитателя 7 через от-(< -2) крытый элемент И поступает значение („2 а на вход сумматора-вычитателя 6 — значей -2) ние Х;2 . Значение, с выхода регистра 2 подается на второй вход сумматоравычитателя 6, где в соответствии со значением оператора (, поступающим из устройства управления на вход 15, суммируется (вычитается) с X<2 (2 . Значение .;+ с выхода сумматора-вычитателя 6 записывается в регистр 2.

Значение Х„ с выхода регистра 1 подается на второй вход сумматора-вычитателя

7, где в соответствии с вычитается (суммируется) с Y„Z, поступающим с выхода элемента И 12. Значение Xq+, получаемое на выходе сумматора-вычитателя

7, записывается в регистр 1, Значение 9< с выхода регистра 3 проходит на вход сумматора-вычитателя 8, где в соответствии с „ вычитается (суммируеч

547765

5 ся) с угловой постоянной А„, поступающей по входу 14 из запоминающего устройства на второй вход сумматора-вычитателя

8. Значение 9 „, получаемое на выходе сумматора-вычитателя 8, записывается в регистр 3 и по выходу 11 поступает в устройство, где используется для определеПроцесс повторяется до выполнения заданного количества итераций. В конце операции результаты Хп+, („+ и gä могут быть выведены соответственно по линиям 9, 10, 11.

При вычислении соотношений (3) работа арифметического устройства аналогична работе в режиме вычисления соотношений (2) с той разницей, что значение Y получается как функция знака, снимаемого в устройство управления с выхода 10. При вычислении величины Е = — значения Хо, х

Х и Z< хранятся соответственно в регистрах 1, 2, 3, а на вход 13 элемента И 12 поступает сигнал запрета.

С началом очередной итерации происходит следующее.

По команде из устройства управления по входу 16 коммутирующий блок 4 соединяет соответствующие выходы регистра 1 с вторым входом сумматора-вычитателя 6 таким образом, что на вход сумматора-вычитателя

=L поступает значение Хц 2, которое в соответствии с складывается (вычитается) со значением Х< из регистра 2. Значение

Х„+ с выхода сумматора-вычитателя записывается в регистр 2 и поступает по выходу 10 в устройство управления для определения значения +

Значение Z, из регистра 3 поступает на вход сумматора-вычитателя 8, где к нему в соответствии с . прибавляет-4 ся (вычитается) величина 2 попадающая на вход 14 из запоминающего устройства.

Значение хо с выхода регистра 1 через сумматор-вычитатель 7 без изменений снова перезаписывается в регистр 1.

На этом итерация заканчивается, и процесс повторяется до выполнения заданного количества итераций, В конце операции результат 2< может быть выведен по линии

11.

Зффективность изобретения заключается в расширении функциональных возможностей арифметического устройства, достигаемом за счет незначительного увеличения затрат оборудования.

Ф ормула и з обретения

1О

Арифметическое устройство, содержащее три сдвиговых регистра, три сумматоравычитателя и два коммутирующих блока, причем выходы всех разрядов первого и второго сдвиговых регистров соединены с соответствующими входами соответственно первого и второго коммутирующих блоков, управляющие входы которых подключены к

ze первому входу устройства, выходы младших разрядов каждого из сдвиговых регистров подключены к первым входам соответствующих сумматоров-вычитателей, выходы которых являются выходами устройства и

2S подключены к входам старших разрядов тех же сдвиговых регистров, выход первого коммутирующего блока подключен к второму входу второго сумматора-вычитателя, второй вход третьего сумматора-вы гитателя

ЗО соединен с вторым входом vcTpDiicTBa, управляющие входы сумматоров-вычитат.елей соединены с третьим входом устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей

35 устройства, оно содержит элемент И, первый вход которого соединен с выходом второго коммутирующего блока, второй вход соединен с четвертым входом устройств;;.. а выход — с вторым входом первого сум4О матора-вычитателя.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 445042, кл, G 06 F 77/ 3388, 1972.

4 2. Патент Великобритании М" 1 331 41 0, кл. (4A, 1973.

3.J. ÅÌîÌ År The СОВИС triPonomet vi C

eompnt< p 1еопп: де ERE Transact ions on heegro

r C Computers,, YE0-8 ¹ 3, 1959 (прототип).

547765

Составитель В, Березкин

Редактор А. Осочников Техред М. Ликович Корректор С. Болдижар

Заказ 877/101 Тираж 818 Подписное

Е1НИИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, -35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4