Функциональный преобразователь кода в частоту

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАЙ ИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

547772 (61) Дополнительное к авт. свид-ву(22) Заявлено 04.06.75 (21) 2141244/24 с присоединением заявки №(23) Приоритет— (43) Опубликовано 25.02.77.Бюллетень № 7 (45) Дата опубликования описания 25.04.77 т,51) М. Кл. (,06 F 15/34

Гасударственный комитет

Совета Министров СССР по делам ивооретений и открытий (53) УДК 681.325 (088.8) (72) Авторы изобретения В. Н. Локтюхин, Г. О. Паламарюк и B. H. Солсмаха (71) Заявитель

Рязанский радиотехнический институт (54) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ КОДА

В ЧАСТОТУ

Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных и управляющих комплексах в качестве нелинейного преобразователя кода в частоту.

Известен функциональный преобразователь (11, содержащий блок определения интервала, вход которого соединен с входом устройства, а выходы подключены через логические элементы И и ИЛИ к входам двух множительно-щ делительных блоков и входу элемента ИЛИ, соединенного другими входами с выходами множительно-делительных блоков, а выходом— со входом частотно-импульсной следящей системы. 15

Недостатком известного устройства является сложность конструкции и необходимость использования дополнительного входного преобразователя код — частоты при работе с входными стенками, представленными gp в цифровой форме.

Прототипом изобретения является функциональный преобразователь кода в частоту

j2), содержащий дешифратор, подключенный входами к шинам старших разрядов входного кода и соединенный выходами со входами блока памяти, двоичный умножитель, соединенный выходом с первым входом основного элемента ИЛИ. выход которого подключен к выхсду преобразователя.

Пониженная точность -.àêîãî преобразователя связана с использованием кусочно-линейной аппоксимации.

Целью изобретения — является повышение точности.

Это достигается тем, что в функциональный преобразователь кода в частоту дополнительно введены коммутатор частот, счетчик, блок сравнения кодов, триггер, частотно-импульсный вычитающий блок, элементы

И и ИЛИ и комммутатор кодов, входы которого связаны с шинами младших разрядов входного кода, а выходы подключены к первым входам блока сравнения кодов, соединенного вторыми входами с выходами счетчика и подключенного выходом к первому входу триггера, второй вход которого соединен с выходом переполнения счетчика, счетный

Bxog KoTopoI o c8238H c BxogoM oIIopHoN i8c

547772 тоты. 11ричем первый выход триггера соединен с первым входом первого элемента И, подключенного вторым входом к первому выходу коммутатора частот, второй выход триггера соединен с первыми входами второго и третьего элементов И, вторые входы которых подключены соответственно к первому выходу блока памяти и второму выходу коммутатора частот, входы которого соединены со вторым и третьим выходами бло- 10 ка памяти и шиной соответствующего разряда входного кода, а выходы первого и второго элементов И подключены ко входам дополнительного элемента ИЛИ, соединенного выходом со вторым входом основного элемента

ИЛИ с суммирующим входом частотно-импульсного вычитаюшего блока, выход которого подключен к счетному входу двоичного умножителя, соединенного цифровыми входами коммутатора кодов, а вычитающий вход — к выходу 20 третьего элемента И.

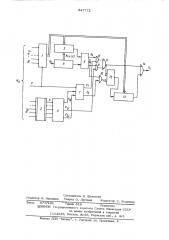

I (а чертеже изображена блок-схема устройства.

Преобразователь состоит из коммутатора

1 кода, дешифратора 2, блока 3 сравнения кодов, счетчика 4, блока памяти 5, триггера 25

6, коммутатора частот 7, элементов И 8-10, элемента ИЛИ 1 1, частотно-импульсного вычитающего блока 12, двоичного умножителя

1 Ы и элемента И!1И 1 4.

Старшие разряды с „(=п-i,»-2,..., -и>-1 вход- 0

1 п.ного кода Nx= - a.; 2, образующие код М0 (=0

1 подключены к дешифратору 2, управляющему блоком памяти 5, 1 азряд и <,>,+,> входного кода подклю-э,, Q. чен к коммутаторам 1 и 7. Младшие разряды a (4 = n— - (m a),...,2,1,0), образующие код КХ -N j подключены к коммутатору кода 1. При С1п,„,„>-— р=С> с коммутатора 1 снимается код К, — g обратный коду

40 х — при С> и „) = = 1 — прямой код Nх,— Я 1, Код, снимаемый с коммутатора 1, поступает на вход блока сравнения кодов Я и двоичного умножителя 1 3.

Другой вход блока сравнения 3 соединен с выходом счетчика импульсов 4, на счетный вход которого подаются импульсы опорной частоть; F Число разрядов счетчика равно p— - (w+ q). Выход блока сравнения

3 и шины переполнения счетчика 4 соответственно подключены к установочным входам триггера 6, Нулевой QX и единичный выход QX триггера 6 подключены соответственно к элемен55 там И 8-10, ко вторым входам которых соответственно подключены частоты F, с выхода блока памяти 5 и частоты Fg и F4 с выходов коммутатора 7 частот Fp u подаваемых на его входы с блока памяти 5.

Выходы элементов И 8 и 9 через элемент

ИЛИ 11 связаны с суммирующим входом вычитающего блока 12, а выход элемента

И 10 — с вычитаюшим входом блока 12, подключенного своим выходом ко входу двоичного умножителя 13. Выходы умножителя 1 3 и элементы ИЛИ 1 1 соединены со входами элемента ИЛИ 14-, выход которого является выходом преобразователя.

Работает функциональный преобразователь следующим образом.

В соответствии со старшими разрядами кода Йо,, определяющего номер участка аппроксимации Npj„h(2>) в котором находится значение входного кода Мх, дешифратор 2 выбирает в блоке 5 необходимые частоты Fpj . Р2 и F4/, моделирующие ординаты 10, g и 4, и подключает их ко входам коммутатора частот 7 и элемента

И U.

Если 1„. N N, то р=д =0 х 1) и-1>»+ ) и на входы блока сравнения 3 и двоичного умножителя 3 поступает код N> — Nx a на входы элемента И 8 и 10 — частоты

oj и ., коммутация которь>х осуществляется коммутаторами 1 и 7, управляемыми сигналом Р С1 („ „

Б течение каждого отрезка времени, равного

= — (1 - )

Р 1 О,»

Т= — дN

1 х о счетчик 4 формирует код hJ($) который линейно- изменяющийся через отрезок времени х î

q 5 N|J

Т х Л о 0 х т ДМХ

Образуемые сигналы С и 1-Q управляют х частотой следования импульсов, поступающих на входы элементов И 8-10 так, что средние значения частоты следования импульсов на их выходах соответственно равны РО Ц„, Fq j gy, и F > (g — Q ), Образуемая на элементе ИЛИ 11 сумма P<>jQ> + F4>(4-QX) поступает на суммирующий вход вычитающего блока 12, а частота Fgj (1"Q ) — на его

X вычитающий вход. сравнивается в блоке сравнения 3 с кодом

Р14 - Nx. ПРи этом тРиггеР 6, на котоРый поступают импульсы переполнения с выхода счетчика 4 и импульсы, появляющиеся на выходе блока 3 в момент равенства кодов, формирует на единичном и нулевом выходах последовательность прямоугольных импульсов скважности

547772

Частота "о,. (г-Юх) " (1-Q„) с выхода блока 12 умножается посредством двоичного умножителя 13 на код N1 — g /дух.

Частота с выхода умножителя 13 суммируется на элементе ИЛИ 14 с частотой с выхода элемента ИЛИ 11 и на выходе ИЛИ 14 образуется результирующая част ота (ö - NÕ)(23 Nx) P .

2(.,)

Noj)(N„Nx) F (дИ )2

Р. (NX NOj)(N43 Х)

2(д )2 23

15

Если 1К < N < Я, то результирующая ц х частота на выходе устройства, работающего аналогично предыдущему случаю, будет равна (N„- N„;)(x» - х) „+

2 (дМ„)2 01 (х 01)(23 х) (д х) (X NOj)(NX N4j ) г. х

Данные зависимости описывают кусочноквадратичную аппр оксимируюшую функцию, которая более точно приближается к заданной функции, чем кусочно-линейная, реализуемая в прототипе.

35

Формула изобретения

Функциональный преобразователь кода в частоту, содержащий дешифратор, подключен- 40 ный входами к шинам старших разрядов входного кода и соединенный выходами со входами блока памяти, двоичный умножитель, соединенный выходом с первым входом основного элеггента ИЛИ, выход которого под- 45 ключен к выходу преобразователя, о т л ич а ю ш и и с я тем, что, с целью повышения точности, в него дополнительно введены коммутатор частот, счетчик, блок сравнения кодов, триггер, частотно-импульсный вычитающий блок, элементы И и ИЛИ и коммутатор кодов, входы которого связаны с шинами младших разрядов входного кода, а выходы подключены к первых. входам блока сравнения кодов, соединенного вторыми входами с выходами счетчика и подключенного выходом к первому входу триггера, второй вход которого соединен с выходом переполнения счетчика, счетный вход которого связан с входом опорной частоты, причем первый выход триггера соединен с первым входом первого элемента И, подключенного вторым входом .к первому выходу коммутатора частот, второй выход триггера соединен с первыми входами второго и третьего элементов И, вторые входы которых подключены соответственно к первому выходу блока памяти и второх;у выходу коммутатора частот, входы которого соединены сс вторым и третьим выходами блока памяти и шиной соответствующего разряда входного кода, а выходы первого и второго элементов И подключсны ко входам дополнительного элемента ИЛИ, соединенного выходом со вторым входом основного элемента ИЛИ и суммирующим входом частотно-импульсного вь читающего блока, выход которого подключен к счетному входу, двоичного умножителя, соединенного цифровыми входами с выходом коммутатора кодов, а вычитающий вход — к выходу третьего элемента И.

Источники информации, принятгяе во BHIIмание при экспертизе:

1. Лвторское свидетельство СССР

М 425182, М.КИ, С 06 Р 15/34 от

07.06. 1 972 г.

2. Потапкин B. К. Функциональный преобразователь частоты в код, "Приборы и системы управления", 1971 г, 4 4, стр. 28 (прототип) .

547772

Составитель И. Шелипова

Редактор Л. Народная Техред О. Луговая Корректор С, Болдижар

Заказ 877/101 Тираж 818 Подписное

)ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

1113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4