Устройство поиска псевдослучайного сигнала по задержке

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11) 547773 (61) Дополнительное к авт. свид-ву— (22) Заявлено 30.06.75 (21) 2150068/24 с присоединением заявки ¹â€” (23) Приоритет— (43) Опубликовано25.02.77,Бюллетень ¹ 7 (45) Дата опубликования описания 26.04.;7 (51) И К °

606 Р 15/36

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий (53) о ДК 681:323, 088.8) (72) Авторы изобретения В. С. Толстяков, Д. О. Яковлев и B. H. Номоконов

Ленинградский ордена Ленина э.-.ектротехнический институт им. В. И. Ульянова (Ленина) (71) Заявитель (54) УСТРОЙСТВО ПОИСКА ПСЕВДОСЛУЧАЙНОГО СИГНАЛА

ПО ЗАДЕРЖКЕ

Изобретение относится к цифровым устройствам обработки сложных сигналов и может быть использовано в связных и радионавигационных системах, модулирующий сигнал которых является двоичным псевдослучайным сигналом (IICC), известным также под названием тп -последовательности или кода максимальной длины.

Задача обнаружения ПСС в таких системах в условиях помех сводится к определению Ið временной задержки принимаемого ПСС, что соответствует определению фазы ПСС и фазированию местного генератора ПСС.

Известны устройства для поиска ПСС по задержке (1), (21, содержащие коррелятор, д соединенный одним из входов с входом устройства, а выходом подключенный к пороговой схеме, ограничитель, связанный с входом первого регистра, подключенного через переключатель к входу второго регистра, раз- 20 рядные выходы регистров через соответствующие сумматоры по модулю два соединены с входами мажоритарного элемента, подключенного через переключатель к другому входу коррелятора. 25

Эти аналоги построены и работают по принципу предварительной оценки фазы и их достоинством является повышенная достоверность оценки фазы за счет исправления ошибок в канале связи, что обеспечивает ускоренный поиск ПСС. Ошибки исправляются с помощью сумматоров и межоритарного элемента.

Недостаток обоих аналогов состоит в том, что для поддержания высокой достоверности оценки фазы при больших вероятностях искажения сигнала необходимо увеличение кратности исправляемых ошибок, а рамках прототипа это возможно только за счет увеличения числа используемых проверок, т. е. существенного увеличения объема аппаратуры — длины регистра, числа сумматоров и сложности мажоритарного элемента. Поэтому при естественных огранияениях объема аппаратурных затрат достижимая достоверность оценки фазы оказывается недостаточной для эффективной работы в условиях сильных помех.

Известно устройство-прототип (31 для поиска псевдослучайного сигнала по задержке, 547773

50 содержащее элемент ИЛИ-НЕ, соединенный с входом счетчика, и последовательно соединенные коррелятор и пороговый блок. Вход коррелятора связан с входом ограничителя и является входом устройства, выход ограничителя — с входом первого регистра, разрядные выходы этого регистра — с первой группой входов блока сумматоров, вторая группа входов которого подключена к разрядным выходам второго регистра, входом соединенного с первым выходом блока переключения, второй выход блока переключения— к управляющему входу коррелятора. Первый вход блока переключения соединен с выходом первого регистра, второй — с соот- 15 ветствующим выходом блока сумматоров, а управляющий вход — с выходом счетчика.

Однако такое устройство не обеспечивает достаточно высокого быстродействия.

Цель изобретения — сокращение времени поиска ПСС по задержке, т. е. повышение быстродействия.

Зто достигается тем, что устройство содержит первый и второй пороговые цифровые элементы и логический блок. Первый и второй входы логического блока соединены с выходами соответственно первого и второго цифровых пороговых элементов, входы которых подключены к соответствующим выходам блока сумматоров, выход первого регистра— с третьим входом логического блока, выход которого подключен к третьему входу блока переключения, а первый и второй входы элемента ИЛИ-НŠ— соответственно с выходами первого и второго цифровых пороговь1х элементов„

Сущность изобретения состоит в обеспечении автоматической остановки процесса исправления ошибок по достижении наиболее достоверной оценки фазы.

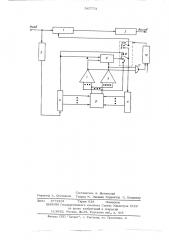

Блок-схема устройства показана на чертеже.

Устройство содержит коррелятор 1, пороговый блок 2, ограничитель 3, регистры сдвига4и5Ä 6 4 и 7, блок сумматоров 8 по модулю два, логический блок 9 выбора сигнала записи, блок переключения 10 — сдвоенный переключатель, двухвходовой элемент ИЛИ-HE 11 и счетчик 1 2.

Входная шина устройства соединена с одним из входов коррелятора 1, выходом подключенного к входу порогового блока 2, выход которого является выходом всего устройства. Вход регистра 4 через ограничитель 3 подключен к входной шине устройства, выход регистра 4 через блок переключения 10 — к входу регистра 5, выходы регистров 4. и 5 — к входам блока сумматора 8 по модулю два, выходы которых соединены с k входами порогового цифрового элемента 6. Параллельно упомянутым k входам порогового элемента 6 подсоединены входы дополнительного порогового элемента

7 с инверторами на входах. Выходы цифровых пороговых элементов 6 и 7 и выход регистра 4 через логический блок 9 выработки сигнала записи и блок переключения 10 подключены к входу регистра 5. Параллельно входам цифровых пороговых элементов 6 и

7 включены входы элемента ИЛИ-НЕ 11, выход которого подключен к шине сброса счетчика 12, входом связанного с тактовой шиной, а выходом — с шиной управления бло-! ка переключения 10. Выход сумматора по модулю два из блока сумматоров 8, подключенного к разрядным выходам регистра 5, соединен через блок 10 с вторым входом коррелятора 1.

Устройство работает следующим образом.

В исходном состоянии положение блокапереключателя 10 соответствует тому, что подвижные контакты переключателя находятся в положении Q и видеосигнал с выхода ограничителя 3 поступает в регистры 4 и 5.

После заполнения всех ячеек регистров 4 и

5 блок переключения устанавливается в положение 5, при этом. на вход регистра 4 продолжают поступать сигналы с выхода ограничителя 3 . На выходах блока сумматоров пэ модулю два вырабатываются сигналы, соответствующие значению разряда С! рео гистра 4, проходящие на входы цифровых пороговых элементов 6 и 7, пороги которых одинаковы и превышают порог мажооитарного элемента

h — °

На выходе порогового элемента 6 появляется сигнал только при условии, если число единичных входных сигналов больше или равно, а на выходе цифрового порогового элемента 7 образуется сигнал, если число нулевых входных сигналов больше или равно (так как входы порогового цифрового элемента 7 инвертированы). Таким образом, назначение цифровых пороговых элементов

Ь и 7 состоит в выработке только наиболее достоверных элементарных символов СС. В связи с тем, что при большой вероятности искажения символов факт превышения порога в цифровых пороговых элементах 6 и 7 имеет место не в каждом такте, то на вход регистра 5 кроме достоверных значений символов поступает часть символов с выхода регистра 4. Запись соответствующих символов с цифровых пороговых элементов 6 и 7 или с выхода регистра 4 проводится с помощью логического блока 9 выбора сигнала записи.

Логический блок 9 вырабатывает сигналы, соответствующие значениям символа Ц, кО547773 торые записываются в регистр 5 в режиме исправления ошибок i5 . Если порог превышен, в элементе 6, то наиболее вероятным значением символа Cl является "1 ", если же порог превышен в элементе 7, то наиболее вероятное значение — "0". Когда нет превышения порога ни в одном цифровом пороговом элементе 6 и 7, то невозможно с повышенной достоверностью судить о значении С и в регистр 5 переписывается зна- 0

G чение CL из последней ячейки регистра 4. о

Если ввести обозначения: У вЂ” сигнал с выхода логического блока 9, к — сигнал с выхода элемента 6, У вЂ” сигнал с выхода элемента 7, z — сигнал с выхода регист-15 ра 4, то функционирование логического блока

9 может быть задано логической функцией

f =у(хч )

Это означает, что при превышении порога Zg в элементе 6 (X 1), логический блок вырабатывает сигнал "1", когда же порог превышен в элементе 7 (У=1), то вырабатывается сигнал "0"; в противном случае, если порог не превышен ни в элементе 6, ни в zs элементе 7, то вырабатывается сигнал, равный выходному сигналу регистра 4.

Таким образом, требуется для построения логического блока эдин инвертор, двухвходовой элемент И и двухвходовой элемент ИЛИ. 30

Выходные сигналы логического блока 9 через блок 10 записываются в регистр 5 до тех пор, пока в n (где n — длина регистра ПС С ) соседних тактах не окажутся сигналы, полученные с помощью пороговых цифровых элементов 6 и 7, т. е. момент записи в регистр

5 достоверных символов ПСС фиксируется с помощью счетчика 12 с коэффициентом пересчета, равным, на вход которого поступают тактовые импульсы, а на шину сбрэ- 40

ca — сигнал с выхода элемента ИЛИ-НЕ 11, вырабатывающего сигнал сброса счетчика

12 с "0" в случае, если на выходах эпемен. тов 6 и 7 сигналы не появляются.

При превышении порогов элементов 6 и

7 в и тактах подряд, т. е. при получении подряд достоверных значений символов ПСС, счетчик 12 переполняется и на его выходе появляется сигнал, переводящий блок переключения 10 в положение э, при котором регистр 5 вместе с цепью обратной связи, замыкающейся через соответствующий сумматор 8 и блок переключения 10, переходит в режим генератора ПСС. При этом выходной сигнал генератора ПСС через блок 10 поступает на вход коррелятора 1 для подтверждения правильности предварительной оценки фазы.

Формула изобретения

Устройство поиска псевдэспучайного сигнала по задержке, содержащее элемент ИЛИНЕ, сэединенный с входом счетчика, и последовательно соединенные коррелятор и пороговый блок, вход коррелятора соединен с входом ограничителя и является входом устройства, выход ограничителя подключен к входу первого регистра, разрядные выходы которого соединены с первой группой входов блэка сумматоров, вторая группа входов которого подключена к разрядным выходам второго регистра, вход которого соединен с первым выходом блока переключения, второй выход которого подключен к управляющему входу коррелятора, первый вход блока переключения соединен с выходом первого регистра, второй — с соответствующим выходом блока сумматоров, а управляющий вход— с выходом счетчика, от лича ющ е ес я тем, что, с целью повышения быстродействия, устройство содержит первый и второй порэгэвые цифровые элементы и логический блок, первый и второй входы которого соединены с выходами соответственно первого и второго цифровых пороговых элементов, входы которых подключены к соответствующим выходам блока сумматоров, выход первого регистра соединен с третьим входом логического блока, выход которого подключен к третьему входу блока переключения, первый и второй входы элемента ИЛИНЕ соединены соответственно с выходами первого и второго цифровых пороговых элементов.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

%447718, кл. G 06 7 15/36, 1973.

2. Авторское свидетельство СССР

N>492883, кл. C 06 F 15/36, 1974.

3. Авторское свидетельство ССС P

%500528, кп. б 06 F 15/36, 1974.

547773

Составитель А. Жовинский

Редактор А. Осочников Техред М. Дикович Корректор С. Болдижар

Заказ 877/1 Ol Тираж 818 Подписное

11НИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раусшкая наб., д. 4/5

Филиал ППП "Патент", г, Ужгород, ул. Проектная, 4