Дешифратор

Иллюстрации

Показать всеРеферат

ggP1«1«.в «, т . ю .1 - б .к".

Q Д И Q A Н И Е с«««в4 увив

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено08.12.75 (21) 2198016/21 с присоединением заявки №(23) Приоритет— (43) Опубликовано25.02.77.Бюллетень № 7 (45) Дата опубликования описания12 07.77 (51) M. Кл

Н 03 К 18/24

Гасударственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.325 (088.8) А. 3. Иванников, А, Д, Кравцов и Ю. Т,.Федоров (72) Авторы изобретения (71) Заявитель (5 ) ДЕШИФРАТОР

Изобретение относится к области вычислительной техники и предназначено для использования в качестве одного из элементов управления матрицей памяти интегрального оперативного запоминающего устройст- 5 ва. Предлагаемый дешифратор позволяет преобразовать полный. двуразрядный код в четырехразрядный, Известен дешифратор, состояший из вход-1О ного и выходного каскадов, выполненный на транзисторах.

Известен также дешифратор, состоящий из двуканального входного каскада, содержашего в каждом из каналов входной трап- 15 зистор, эмиттер которого подключен Ко вхо.ду дешифратора, коллектор соединен с базой переклточающего транзистора входного каскада, а база входного транзистора соединена через резистор с шиной питания и выходного каскада, выполненного на транзисторах и диодах.

1Яель изобретения — снижение потребляемой мощности и повышение надежности, дешифратора. 25

ЭтО ДОСтИГаЕтСН тЕМ, ЧВО В ДЕШ.IPPaTOPe, состоя нем из двуканального входного каскада, содерм ащего В каждом из каналов входH0II транзистор, эми Тер котopoi 0 НОдключен ко входу дешифратора, кOJIJIe«TOp соединен с базой переключатешего транзистора, а база входного транзистора соединена через pt я«стор с шиной IIvTaiiz;I и выходного ка"када,выполненного на трап;исторах и .Ion»х коллектОР ПЕРЕКИОЧаЮШЕГО тРан»ИСЧ .1 с -: I iil .: ОГО каскада подключен «обшей ш . ;.е-, э, »т гор через резистор — к шине ш«тания, к «атодам

Соот»ЕВСтВуЮШИХ дпэдОВ ВЬ:Хост, ОГО КОС.«ад», а также к аноду дпс«да, катод «торого соединен с Оазой инвертпруюнк I 0 го«, .Ilзисто(ш, причем коллектОр ннвертиру«с«с «го транзисT0PG ПОДКЛЮЧЕН K 06НСЕЙ Н!Инс-„Э. .«Нтт с Р «ЧЕрез резистор — к ш: не питания и к «атодам соотВетствуюших диодов Выходного кас«ада, при этом ооьединенпые попарно «под»с диодиых пар выходного каскада под . почены ч рез ðe&PC"I Ор, К ШИНЕ ПИтаНИя И «сн .Н;-«,. сподО«З, катоды которых подключесны «б- .—::, соот»етствуюших транзисторов Вых днсг: « ..;, .д i, «Оллекторы последних соединены с .«б,цей инной, 547968 а эмиттеры — с соответствующими выходами дешифратэра.

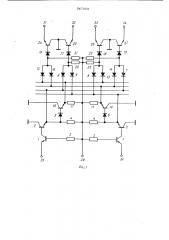

На фиг. 1 показана принципиальная схема предлагаемого дешифратора; на фиг. 2 — временные диаграммы прэхождения импульсных сигналов на входе и выходе устройства.

Дешифратор содержит в каждом канале входного каскада входной транзистор 1, эмиттер котэрогэ подключен к соответствующему входу дешифратора База транзистора 1 через lo резистор 2 соединена с шиной питания. Коллектэр транзистора 1 подключен к базе переключающего транзистора 3, коллектор котэ рэгэ связан с эбщей шиной. Эмиттер транз> стэра 3 через резистор 4- подключен к п>ине питания, к аноду диода 5 и к катодам диэдэв 6 и 7 для левого канала, 8 и

9 для правэгэ канала выходнэго каскада, Катод диода 5 связан с базой инвертируюшегэ транзистора 10, коллектор кэторэгэ соединен с обшей шиной. Эмиттер тран, »стора 10 через резистор 11 подключен к шине питания и к катодам диодов 12 и 13 выходного каскада для левэгэ канала и 14 и 15 для правого канала.

Объед»неннь>е аноды диодных пар 12 и

15,6 и 9,8 и 13,7 и 14сэединеныс анодами диодов 16 и 17, 18 и 19 соогветственно и через резисторы 20 и 21, 22 и 23 с шиной питания. Катоды диодов 16 и 17, 18 и 19 связань> с базами выходных транзисторов 24 и 25, 26 и 27 соответственно. К сллекторь> транзисторов 24, 25,26 и 27 объединены и подключены к эбщей шине. Шина питания 28, входы

35 дешифратора 29,30. Змиттеры этих транзисторов подключены к сэответствуюшим выходам дешифратора 31-34, Дешифратор рабэтает следующим эбразом.

Пусть на входы 29 и 30 поданы сигна40

;>и логической "1 " (3; „ 2,4д), В этом случае TOK протекает по цепи резистор 2— транзистор 1 (база-коллектор)- транзистор

3 (база-коллектэр) в каждом канале вход45 нэгэ каскада и далее на обшую шину. Коллектэрные переходы транзисторов 3 смещаются в прямом направлении, а транзистэры переходят в насыщенное состояние, При этом потенциалы на эмиттерах транзисторов 3 составляются, и — О. Ток в цепи диод 5 — транзисторы 10 (база-коллектор) отсутствует, и транзисторы 10 заперты.

Через резистэр 20>, диэды 6 и 9, резистор 22, диод 8 и резистор 23, диод 7 и насыщенные транзисторы 3 обоих каналов ток протекает на обшую шину, Диоды

12 и 15 заперты потенциалами эмиттеров закрыть>х трапзисторов 10. Ток через резистор ?1 пэ цепи резистор 21 — диод

16 — транзистор 24 (база-коллектор) замыкается на обшую шину. Транзистор 24 переходит в насьнненное состояние. Транзисторы 25,26,27 заперты (базовый ток отсутствует) и уровни потенциалов на эмиттерах соответствуют логической "1".

Пусть теперь на один из входов дешифратора (например 29) подан сигнал логическойй "1", а на другой (30) — логического "0". В этом случае ток прэтекае> по цепи резистор 2 — транзистор 1 (базаколлектор) - транзистор 3 (база-коллектор) левого канала входного дешифрируюшего каскада, а далее на общую шину.

Коллекторный переход транзистора 3 это>.o канала смешается в прямом направлении, а транзистор переходит в насышенное состояние. При этом потенциал на эмиттере транзистора 3 составит U — О. Ток в цепи диод 5 — транзистор 10 (база-коллектор) отсутствует, и транзистор 10 заперт. Через резистор 20, диод 6, резистор 23, диод 7 и насышенцый транзистор 3 левогэ канала ток протекает на обшую шину. Диоды 12 и 13 заперты потенциелэм на эмиттере закрытого транзистора 10 левого канале. Р тэ же время в правом канале TOK прэтекаег по цепи резистор 2 — переход база-эмитгера транзистора 1 и вход устройства на эбшую шину. Транзистор 3 переходит в закрытое состояние, и потенциал на эмигтере примерно равен потенциалу источника питания E Ток протекает по цепи диод 5—

t1 транзистор 10 (база-коллектор) правого канала на общую шину. Транзистор 10 правого канала переходит в .ненасыщенное состояние, потенциал его эмиттера U„„O. Тогда тэк через эезистор 21, диэд 15, а также через резистор 23 диод 14 и открытый транзистор 10 гравэго канала протекает на обшую шину. При этом диоды 8 и 9 заперты высоким потенциалом на эмиттере закрытого транзистора 3 правого канала, Поскольку из четырех диодных пар только пара диодов

8 и 13 находится в закрытом состоянии, ток прэтекаеr через резистор 22, диод 18, переход база-коллектор выходного транзистора 26 на обшую шину. Транзистор 26 переходит в насыщенное состояние, и óðîвень потенциала на его эмиттере соответствует "0", а транзисторы 24, 25 и 27 заперты (базовый ток отсутствует) и уровни потенциала на их эмиттерах соответствуют л огическ ой " 1 ", Таким образом, двуразрядный код на входах дешифратора преобразуется в четырехразрядный адресный код на выходах в соответствии с таблицей HcrHHHocrè.

547968

Из рассмотрения работы устройства вытекает, что при любых комбинац..ях сигнаl5

JIoB ца входах только на одном выходе будет низкий уровень потенциала, и при выборе одной схемы из четырех неооходим один логический вход в управляемой схеме, 20 ф ор мула из обре re ния

Дешифратор, состоящий из двук".нального входпого каскада, содержащего в каждом из каналов входной транзистор, эмиттер которого подключен ко входу дешифратора, коллектор соединен с базой переключающего трап;зистора, а база входного транзистора соединена через резистор с шиной питания и выходного каскада, выполненного на транзисторах и диодах, о т л и ч а ю ш и й— с я тем, что, с целью снижения потребляем ой м ощности и повышения надежи ости, коллектор переключающего транзистора входного каскада подключен к обшей шине, эмиттеры через резистор — к шине питания, к катодам соответствующих диодов выходного каскада, а также к аноду диода, катод которого соединен с базой инвертирующего транзистора, причем коллектор инвертируюшего транзистора подключен к общей шине, эмиттер через резистор — к шине питания и к катодам соответствующих диодов выход-. ного каскада, при этом объединенные попарНо аноды диодов BbfxDQHol каскада lIQLLKJIK — чены через резистор к шине питания и к анодам диодов, катоды которых подключены к базам соответствующих транзисторов выходного каскада, коллекторы последних соединены с общей llIHHQH, а эмиттеры - с соответствующими выходами дешифратора, 547968

Составитель Г Кутний

Редактор Астафьева Техред М. Левицкая Корректор А. Гриценко

Заказ 1196/109 Тираж 1065 Подписное

LlHHHHH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, ?K-35, Рауш кая наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул Г зсектная, 4