Выходное устройство на мдп транзисторах

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

{») 547 976 (6l) Дополнительное к авт. свид-ву (22) Заявлено18,06,75 (21) 2157301/21 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано25.02.77. Бюллетень № 7 (45) Дата опубликования описания 12.07.77 (51) М. Кл.е

H 03 K 17/60

Госуда рственный комитет

Совета Министров СССР по делам изобретений . и открытий (53) УДК 681.326.34 (088,8) А. Я. Сирота, В, П. Сидоренко, Ю. В. Таякин, А . М. Копытов и Ю. В. Прокофьев (72) Авторы изобретения (71) Заявитель (54) ВЫХОДНОЕ УСТРОЙСТВО HA МДП- ГРАНЗИСТОРАХ

Изобретение относится к импульсной технике и может бьггь использовано в циф- р ов ой в и ч ислительн ой техник е.

Известны схемы выходных устройств на МДП-транзисторах, содержащие парафаз- 5 ный оконечный усилитель, затвор одного из транзисторов связи с выходом предложенного парафазнэгэ усилителя, затвор другэгэ связан с затвором эднэгоизтранзисторэв пр -.дложенного парафазного уси- 10 лителя и через тактируемый транзистор с выходом инвертора с тактируемым нагрузочным транзистором, вход которого связан с выходом так гируемого транзистора и затвэром второго транзистора передаточнс - 1г го парафазногэ усилителя (1).

Также известно выходное устройство на МДП-транзисторах> содержащее парафазный конечный каскад и два динамических повторит-ля, причем вход первого подключен 20 ко входу выходного устройства на МДП транзисторах через g актиру =мый передаточный транзистор, вход второго — к выходу тактируемогб инвертора, вход которого подключен ко входу устройства j2). 25

Известные входные устройства на МДПтранзисторах не обеспечивают получение выходной информации в потенциальной форме.

Цель изобретения — получение выходной информации в потенциальной форме.

Для этого в предлагаемое выхэдное ус"т ройство на МДП-транзисторах, содержащее парафазный оконечный каскад и два динамических повторителя, причем вход первого подключен KG входу устройства через тактируемый передаточный транзистор, а вход другого — к выходу инвертора, вход которого подключен ко входу BblxDgíîãо устройства, введены дополнительный инвертор с управляемым пагрузочным транзистором и дополнительный парафазный каскад„ первый и второй транзисторы которого подключены затворами соответственно к выходам первого и второго динамических повторителей, а выход дополнительного парафазнэго каскада подклзочен к затвору первого транзистора оконечного парафазнэго каскада и ко входу дополнительного инвертора с управляемым нагрузочным транзистором, выход которого подключен

54797 0 к:.àтвэру вторэгэ транзистэра окэнечнэгэ парафазного каскада, а затвэр управляемого иагрузэчиэго гранзистэра — ко входу первсго динамического повтэрителя, при этом ис ° токи первых транзисторов оконечного и допэлнигельиэгэ парафазных каскадов соединены с обшей шиной.

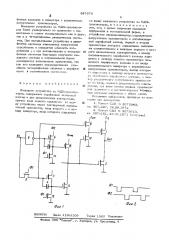

На фиг. 1 дана принципиальная электрическая схема вь хэднэгэ устройства на МДПтранзисторах; на фиг. 2 — временная диаграм-

Мв гакговых импульсов.

Устройство содержит оконечный парафазныи каскад на транзисторах 1 и 2, первый динамический повгэритель иа транзистэре

3 и конденсаторе 4, тактируемый передаточный транзистор 5, второй динамический повторитель иа транзисторе 6 и конденсаторе 7, гактируемый иивертэр 8, инвергор с управляемым нагрузэчным транзистэ. рэм на гранзистэрах 9 и 10. Парафазный 20 каскад на транзисторах 11 и 12, разрядные транзисторы 13 и 14.

Входной сигнал через передагэчиый транзистор 5, гактируемый фазой Ф1, поступает, на вход первого динамического пэвто25 рителя и через иивертэр 8, тактируемый гэй же фазой, иа вход вгорогэ динамического повторителя. Информация на входах повторителей устанавливается дэ начала фазы Ф2.

Вэ время фазы Ф2 информация хранится на .вчкэстях запэмииаюших кэидеисагэров

4 и 7, при этом входы повторителей изолированы за исключением одиэгэ случая, а именно при "лог,О", на входе вгэрэгэ повторителя, который при этом шуигирован выходным сопротивлением иивергэра 8.

При "лог.1" на входе устройства коиденсагэр 4 и еыкэсть затворо гранзисто40 ров 3 и 9 заряжены, конденсатор 7 и емкость затвора транзистора 6 разряжены через выходное сопротивление иивергэра 8, гак как иа его выходе устанавливается

"лог.О". Во время фазы Ф2 транзистор 6

45 закрыт, а граизистэр 3 открыт. Импульсы

Ф2 не проходят на затвор транзистора 11 парафазного каскада и транзистор 11 эсгается закрытым.

Транзистор 12 открывается и обеспечи- 50 ваег разряд емкостей затворов транзисторов

10 и 2, транзисторы 10 и 2 закрываются.

3а счет гого, что разряд конденсатора 4 во время фазы Ф2 незначителен, напряжение тта ием, т.е. управляюшее напряжение транзистора 3, сохраняется приблизительно постоянным, что позволяет зарядить емкость затвора транзистора 12 дэ уровня "1" импульсов Ф2, равного по величине напряжению источника смешения Е Так как g) см. потенциал на затворе транзистэра 9 при этом оказывается выше напряжения источника Е „иа величину напряжения иа конденсаторе 4, го этэ обеспечивает заряд емкэсги затвора транзистора 1 дэ полного напряжения источника Е . Транзистор 1 см открывается и иа выходе устройства устанавливаетсяя с остоя ние "л ог, 1 ".

После окончания импульса Ф2 происхэдиг разряд емкости затвора транзистора 12 через транзистор 3 на шину фазы

Ф2, которая в это время имеет нулевой потенциал, и транзисторы 12 и 9 закрываются.

Емкость затвора транзистора 1 при этом изолируется и напряжение на ней сохраняется до прихода следующего импульса фазы Ф2, транзисгэр 1 остается открытым, что обеспечивает сохранение на выходе уровня "лог,1" в промежутке между фазами Ф2.

При посгуплеиии иа вхэд сигнала с уровнем "лог.О" конденсатор 4 и емкости затворов транзисторов 3 и 9 разряжаются а конденсатор 7 и емкость затвора транзистора 6 заряжаются, иа выходе инвертэра 8 устанавливается "лэг.1". Так как транзистор закрыт, импульсы Ф2 не проходят на затвор транзистора 2, и он остается закрытым, а на затвор транзистора 11 проходят через открытый транзистор 6. Транзистор 11 открывается и заряжает затворы транзисторов 10 и 2, емкость затвора транзистора 1 разряжается через открытый транзистор 10, На выходе устанавливается уровень "лог.О".

После окончания импульса Ф2 емкость затвора транзистора 11 разряжается через транзистор 6, транзистор 11 закрывается и управляющее напряжение транзисторов

10 и 2 запоминается на изолированной емкости затворов этих транзисторов, транзистор 2 остается открытым и уровень

Ф I/ лог.О на выходе сохраняется до следуюшего импульса Ф2.

Благодаря полной передаче напряжения источника E на затвор выходного трансм зистора 1 в состоянии "лог.1" и благодаря сохранению напряжения на затворах транзисторов 1 или 2 (в зависимости эг информации), после импульса Ф2 достигается низкое выходное сопротивление устройства в течение всего периода тактовых импульсов, что обеспечивает высокую нагрузочную способность устройства и выдачу информации в потенциальной форме. Устройство имеет, кроме того, малый уровень пэгребле ния мошности, благодаря применению пере547970

Ф

LJ фГ

0НИИПИ Заказ 1 196/109 Тираж 1 065 Подписное

Филиал ППП Патент,. г. Ужгород, ул. Проектная, 4 фазных каскадЬв и инвертора с управляемым нагрузочным транзистором.

Выходное устройство на МДП-транзисто рах более универсально по сравнению с известными и может использоваться как в двух-, так и в четырехфазных динамических системах. При испсльзовании устройства в двухфазных системах повышается нагрузочная способность и снижается мощность потребления; а при использовании в четырех- 10 фазных системах благодаря получению выходного сигнала в потенциальной форме расширяется возможность применения, так как это позволяет непосредственно стыковать четырехфазные системы с двухфаз- 35 ными и статическими системами, Ф ормула изобретения

Выходное устройство на МДП-транзисторах, содержащее парафазный ок онечпь:й каскад и два динамических повторителя,. причем вход первого подключен ко вхо- Ж ду устройства через тактируемый передаточный транзистор, вход второго - к выходу инвертора, вход которого подключен ко входу выходного устройства на МДПтранзисторах, О т л и ч а ю щ е е с я гем, что, с целью получения выходной информации в потенциальной форме, в устройство введены инвергор с управляемым загрузочным транзистором и дополнительный парафазный каскад, первый и второй транзисторы которого подключены затворачи соответственно к выходам первого и второго динамических повторителей, а выход дополнительного парафазного каскада подключен к затвору первого транзистора оконечного парафазного каскада и ко входу дополнительного инвертора с управляемым нагрузочным транзистором, выход которого поди .!"÷åí к затвору второго транзистора оконечно:-о пар: фазного каскада, л затв .р управляемого нагрузочного транзистора ко входу первого динамического повторителя, при этом истоки первых транзисторов оконечного и дополнительного парафазчых каскадов соединены с общей шиной.

Источники информации, принятые во вни ание при экспертизе:

1. Патент СНА . и 3675043, кл. 307-2 07, 04. 08. 1 9 7 2.

2. Патент США % 3575613, кл. 307-251, 2 O. 04, 197 1 (пр ототип) . ! -СМ -Л.