Отсчетное устройство

Иллюстрации

Показать всеРеферат

О П И С А Н И Е п) 548858

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1. (51) M. Кл.- G 06F 7/38 (61) Дополнительное к авт. свид-ву (22) Заявлено 31.05,74 (21) 2031237/24 с присоединением заявки № (23) Приоритет

Государственный комитет

Совета Министров СССР но делам изобретений Опубликовано 28.02.77. Бюллетень ¹ 8 (53) УДК 681.327(088.8) и открытий

Дата опубликования описания 30.03.77 (72) Авторы изобретения

А. М. Клинов, Ю. E. Тарнавский и И. М. Гольтман

Одесское конструкторское бюро кинооборудования (71) Заявитель (54) ОТСЧЕТНОЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники и может быть использовано в арифметических устройствах программного управления, в вычислительных машинах и цифровых измерительных приборах.

Известно отсчетное устройство, содержащее генератор опроса, логические элементы, усилители, дешифратор.

Недостатком его является то, что оно может быть использовано только для стробоскопического питания цифровых индикаторов.

Наиболее близким техническим решением к изобретению является отсчетное устройство, содержащее многоразрядный реверсивный двоично-десятичный счетчик, тактовый генератор, выход которого соединен с входом тактового распределителя, выход которого соединен с входами первого коммутатора, выходы которого соединены соответственно с первой группой входов блока цифровых индикаторов, вторая группа входов которого соединена с выходами второго коммутатора, входы которого соединены с выходами дешифратора.

Такое устройство имеет ограниченные функциональные возможности, так как используемая в нем аппаратура предназначена только для стробоскопической индикации.

Целью изобретения является расширение функциональных возможностей устройства.

Цель достигается тем, что в устройство введены переключатель ввода, шифратор, блок реверсивных двоичных счетчиков, де5 сятичный сумматор, триггер запоминания переноса, триггер переключения режимов, триггер запоминания ввода, элемент И, блок элементов И и блок кольцевых регистров, шины сдвига которых соединены с выходом тактово10 го генератора и со счетным входом триггера запоминания переноса, вход управления и выход которого соединены соответственно с выходом и входом переноса десятичного сумматора. Выходы блока кольцевых регистров

15 соединены с первыми входами блока элементов И, выходы которых, а также выходы шифратора соединены с соответствующими входами слагаемых сумматора, выходы которого соединены с входами управления блока коль20 цевых регистров, а также с входами дешифратора, выходы тактового распределителя соединены с входами блока переключателей ввода k-й (где k=1, ..., и) выход тактового распределителя соединен с первым входом

25 элемента И, à (k+/)-й выход с входами установки в «О» триггера переключения режимов и триггера запоминания команды «Ввод».

С вторым входом элемента И соединен единичный выход триггера запоминания команз0 ды «Ввод», выходы реверсивных двоичных,1 Я г" "

3 счетчиков и выход блока переключателей ввода соединены с разрядным входом шифратора, вход .управления которого, а также вторые входы блока элементов И соединены с выходом триггера переключения режимов, вход установки в «1» которого соединен с выходом элемента И.

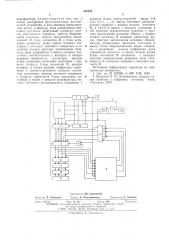

На чертеже показана блок-схема предлагаемого устройства.

Отсчетное устройство содержит тактовый генератор 1, выход которого соединен с входом тактового распределителя 2, с шинами сдвига блока кольцевых регистров 3 и со счетным входом триггера запоминания переноса 4. Вход управления и выход триггера запоминания переноса 4 соединен соответственно с выходом и с входо»I переноса дссятичного сумматора 5.

Выходы блока кольцевых регистров 3 соединены с первыми входами блока элементов

И б, выходы которых, а также выходы шифратора 7 соединены с входами слагаемых десятичного сумматора 5. Выходы десятичного сумматора 5 соединены с входами управления блока кольцевых регистров 3, а также с входами дешифратора 8. Выходы дешифратора 8 соединены с входами второго коммутатора 9, выходы которого соединены с катодами блока цифровых индикаторов 10. Аноды блока цифровых индикаторов 10 соединены с выходами первого коммутатора 11, входы которого соединены с шинами тактового распределителя 2.

Выходы тактового распределителя 2 соединены с шинами переключателей ввода 12, А-й выход тактового распределителя 2 соединен с входом элемента И 13, à (k+l)-й выход— с входами установки в «О» триггеров переключения режимов 14 и запоминания ввода

15. С другим входом элемента И 13 соединен единичный выход триггера запоминания ввода 15. Выходы блока реверспвных двоичных счетчиков 1б и шины переключателей ввода

12 соединены с входом шифратора 7, шина управления которого, а также входы блока элементов И б соединены с выходом триггера переключения режимов 14, вход установки в «1» которого соединен с выходом элемента

И 13.

Устройство работает следующим образом.

Импульсами от тактового гснератора 1 запускается тактовый распределитель 2, включается для циркуляции числа блок кольцевых регистров 3 и триггер запоминания переноса 4.

Если блок элементов И открыт, то в цепи десятичный сумматор 5 — блок кольцевых регистров 3 циркулирует число, ранее зафиксированное параллельным в пределах тетрады кодом. По поступлении команды «Ввод» опрокидывается в «1» триггер запоминания ввода 15, который разрешает прохождение через элемент И 13 k-го импульса тактового распределителя 2. Этот импульс опрокидывает в «1» триггер переключения режимов 14, 5

50 прп этом (k+1), (:+2), ..., (k+l)-мп импульсами через контакты 1, 2, ..., и переключателей ввода 12, и ифратор 7 и десятичный сумматор 5 в блок кольцевых регистров 3 вводятся потстрадно двоично-десятичные коды чисел, набранные подвижными контактами перскл.очателей вво".à 12 (l — число разрядов вводимого числа), (/г+1) -й импульс тактового распределителя 2 опрокидывает и

«О» триггер запоминания ввода 15 и триггер переклю еппя режимов 14. Ввод по этому каналу прекращается, и в блоке кольцевых регистров 3 циркулирует введенное число. Потенциалы находяи1ейся в данном такте на выходе десятичного сумматора 5 тетрады через депгифратор 8 и коммутатор 9 открывают соответствующие катоды блока цифровых индикаторов 10, один пз которых зажигается разрядом емкости первого коммутатора 11, управляемого от тактового распределителя 2.

Между пмпульсамп считывания блок реверспвных двоичных с гетчпков 1б накапливает поступающие на него импульсы входной информации. (/г+1), (1+2), ..., (/г+1) -ми импульсами код малоразрядных реверсивных двоичных счетчиков блока 1б через десятичный сумматор 5 в завис. мости от знака суммирустся с кодом чисел блока кольцевых регистров 3, либо вы штается из него, при этом блок реверсивных двоичных счетчиков 16 очищается этими же импульсами и далее может накапливать информацию до очередного считывания, Такое выполнение схемы устройства позволяет фиксировать малоразрядными реверсивными двоичнымп счетчиками определенное число регистрируемых отсчетных импульсов в промежутке времени между очередными тактами распределителя, а затем параллельным кодом вводить в качестве первого слагаемого на вход десятичного сумматора и суммировать с цпркулируемым параллельным кодом кольц".âûõ регистров — элементов памяти стробоскопической индикации.

Таки;I образом, изобретение позволяет значительно расин, рить функциональные зозможности отсчетного устройства, а именно с помощью десяти ного сумматора и аппаратуры, предназначавшейся в известных устройствах только для стробоскоппчсской индикации, осуществляется основной реверспвный отсчет регистрируемой в двопчно-десятичном коде информации.

Формула изобретения

Отсчетное устройство, содержагцее тактовый генератор, выход которого соединен с входом тактового распределителя, выход которхо соединен с входамп первого коммутатора, выходы которого соединены соответственно с первой группой входов блока цпфровь х индикаторов, вторая группа входов которого соединена с выходами второго коммутатора, входы которого соединены с выходами

548858

Составитель Ю. Тарнавский

Текред А. Камыи никова

Корректор Е. Хчелсва

1 едактор T. Рыбалова

Заказ 435/13 Изд. ¹ 247 Тираж 899 Подписное

Ц11ИИПИ (осударствеиного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж35, Раугиская H",á., д 4/5

Типография, пр. Сапунова, 2 дешифратора, отлича ющееся тем, что, с целью расширения функциональных возможностей устройства, в него введены переключатель ввода, п1ифратор, блок реверсивных двоичных счетчиков, десятичный сумматор, триггер запоминания переноса, триггер переключения режимов, триггер запоминания ввода, элемент И, блок элементов И и блок кольцеаих регистров, шины сдвига которых соединены с выходом такгового генератора и со счетным входом триггера запоминания переноса, вход управления и выход которого соед,1нены соответственно с выходом и входом переноса десятичного сумматора, выходы б.дока кольцевых регистров соединены с первымп входамп блока элементов И, выходы которых, а также выходы шифратора соединены с соответствующими входами слагаемых сумматора, выходы которого соединены с входами управления блока кольцевых рег:.стров, а также с входами дешифратора, выходы тактового распределителя соединены с входамп блока перекл1очателей ввода, k-й (где k=1, ..., и) выход тактового распределителя соединен с первым входом элемента

И, а (k+1) -й выход с входами установки в

5 «О» триггера переключения режимов и триггера запоминания команды «Ввод», с вторым входом элемента И соединен единпчньш выход триггера запоминания команды «Ввод», выходы реверспвных двоичных счетчиков и

10 выход блока переключателей ввода соединены с разрядным входом шифратора, вход управления которого, а также вторые входы блока элементов И соединены с выходом триггера переключения режимов, вход уста15 нонки B «1» которого соединен с выходом элемента И.

Источн41ки информации, принятые во внимание прп экспертизе:

1. Авт. св. № 222006, G 06F 7/38, 1965.

20 2. Швецкий Б. И. Электронные измерительные приборы с цифровым отсчетом, Киев, «Техн и к а», 1970.