Устройство для управления тиристором

Иллюстрации

Показать всеРеферат

(орооювнфет

-.;; и,ч я ЯЕЯ . .::,.1 т,е,; -. Ц.ъ А

ОП ИСА НИ Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ п1 548933

Соез СоветскихСециалистнческик

Реепублик (61) Дополнительное к авт. свид-ву (22) Заявлено 22.12.75 (21) 2301357/07 с присоединением заявки № (51) М. Кл. H 02Р 13/16

Государственный комитет

Совета Министров СССР ио делам изобретений и открытнй (23) Приоритет

Ф

Опубликовано 28.02.77. Бюллетень № 8 (53) УДК 621.316.727 (088.8) Дата опубликования описания 08.04.77 (72) Авторы изобретения Ю. Д. Альгин, И. М. Осипова, Л. В. Ребров и В. Н. Губарев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ТИРИСТОРОМ

Изобретение относится к области преобразовательной техники и может быть использовано в системах управления преобразовательных устройств на тиристорах, наличие реактивностей и разнообразие режимов в цепях нагрузки которых требуют повышения устойчивости включения тиристоров.

Известные схемы управления тиристорами пачками импульсов фиксированной длительности (1), работающие по принципу конечного автомата, не обеспечивают в полной мере оптимальных условий устойчивости включения тиристора.

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство (2), содержащее последовательно соединенные блок для синхронизации управляющего сигнала с сетью, фазосдвигающий блок, состоящий из триггера, первый вход которого подключен к выходу блока для синхронизации управляющего сигнала с сетью, блок сравнения — балансный диодно-регенеративный компаратор — и усилитель мощности управляющих импульсов.

Наличие управляющих импульсов после включения тиристора приводит к увеличению рассеиваемой мощности тиристора, снижению его надежности и снижению экономичности канала управления.

Целью изобретения является повышение надежности тиристора. Поставленная цель достигается тем, что устройство снабжено дополнительным формирователем сигнала, причем анод тирпстора через указанный формирователь подключен на второй вход триггера.

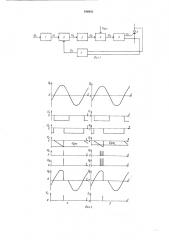

На фиг. 1 изображена блок-схема устройства управления тиристором пачками импульсов с дли гельностью, ограниченной включением тиристора; на фиг.2 — диаграмма напряжения, характеризующая работу элементов устройства.

Синхронизация работы канала управления тир и стор ом осуществляется блоком 1, преобразующим переменное сину соидальное напряжение сети в прямоугольное. Выход блока 1 соединен с одним из входов триггера 2, выполняющего функцию хронирующего эле20 мента фазосдвигающего устройства и управляющего работой ключевого элемента в генераторе пилообразного напряжения 3.

Выход генератора 3 соединен с одним из

25 входов блока сравнения — балансного диодно-регенеративного компаратора 4, — на второй вход которого подано управляющее напряжение К-,р, изменяющееся в соответствии с задачами регулирования преобразова30 тельного устройства.

548933

Выход компаратора подключен ко входу выходного устройства 5, где сигнал управления тиристором 6 усиливается по мощности.

Лнод и катод объекта управления — тиристора 6, — через цепь формирования сигнала

7 подключены ко второму входу триггера 2, что обеспечивает работу канала по замкнутому циклу.

В нормальных условиях, когда в силовых цепях преобразовательного устройства существуют все условия для включения тиристора с подачей на него сигнала управления элементы схемы фиг. 1 функционируют следующим образом.

B момент перехода синусоиды U, через нуль (фиг. 2, а) соответствующее прямоугольное напряжение Ui с выхода блока синхронизации 1 подается на один из входов триггера 2, вызывая его переключение (U на фиг. 2, а). В момент переключения мгно- 20 венного значения напряжения пилообразной формы (Уз) и напряжения управления (U>>p), подаваемых на разные входы компаратора 4, последний возбуждается и начинает генерировать импульсы. Первый импульс (U4 на фиг. 25

2, а), образовавшийся на выходе компаратора, после усиления по мощности в блоке 5 (Uq) подается на управляющий электрод тиристора

6. В момент перехода тиристора в проводящее состояние напряжение на его аноде U< З0 скачком падает до нуля. Указанное изменение анодного напряжения тиристора с помощью формирующей цепи 7 преобразуется к виду, необходимому для переключения триггера 2 (U7) в первоначальное состояние. 35

Одновременно с возвратом триггера ключевой транзистор генератора пилообразного напряжения 3 переводится в проводящее состояние и дальнейшее генерирование пилы прекращается. Происходит быстрый разряд 40 интегрирующей емкости через малое сопротивление открытого транзистора. Со срывом пилообразного напряжения исчезают условия для возбуждения балансного диодно-регенеративного компаратора 4. Дальнейшее гене- 45 рирование импульсов на его выходе прекращается. Единственный импульс, образовавш ийся в блоке 4, после усиления используется для управления тиристором, а перепад напряжения на последнем — для возврата 50 фазосдвигающего устройства в исходное состояние.

Если к требуемому для переключения тйристора моменту времени не создались условия для его коммутации, первый импульс, образованный на выходе компаратора 4 (U4 на фиг. 2, б) и соответствующий ему импульс на управляющем электроде (Us) не смогут открыть тиристор. В этом случае не появится условий для перевода схемы в исходное состояние и пилообразное напряжение (Ua) выйдет за уровень напряжения управления (У,-„р). В компараторе сохраняются условия возбуждения, и на выходе образуется серия импульсов с частотой, определяемой его параметрами, Как только в силовой цепи тиристора будут достигнуты условия коммутации, очередной импульс из генерируемой серии включает его. Триггер 2 возвращается в исходное состояние, и генерирование импульсов управления тиристором прекращается.

Использование изобретения позволит при высокой устойчивости коммутации тиристоров в преобразовательных устройствах повысить надежность тиристоров и экономичность канала у"правления.

Формула изобретения

Устройство для у правления тиристором пачками импульсов с длительностью огран иченной включением тиристора, содержащее последовательно соединенные блок для синхронизации управляющего сигнала с сетью, фазосдвигающий блок, состоящий из триггера, первый вход которого подключен к выходу блока для синхронизации управляющего сигнала с сетью, блок сравнения и усилитель мощности управляющих пмпульсов, отл и ч а ю щ е е с я тем, что, с целью повышения надежности тиристора, оно снабжено дополнительным формирователем сигнала, причем анод тиристора через указанный формирователь подключен на второй вход триггера.

Источники информации, принятые во внимание при экспертизе:

1. Лвт. св. № 228119, кл. Н 02Р 13/16, 1966.

2. Лвт. св. № 233043, кл. Н 02Р 13/16, 1968 (прототип) .