Устройство для преобразования двоично-десятичного кода в двоичный

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<»>54980l (61) Дополнительное к авт. свид-ву— (22) Заявлено 06.08.74 (21) 2049852/24 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 05 03.77. Бюллетень ¹ 9 (45) Дата опубликования описания 27.07.77 (51) М.Кл G 06 F 5/02

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681 3 (088.8) (72) Авторы изобретения А. М. Полищук, В. П. Распутный и Л. И. Сальникова (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ

ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ

Устройство относится к области вычислительной техники и может быть использовано в ЭВМ и устройствах, где необходимо преобразование информации из двоично-десятич ной системы счисления в двоичную.

Известны устройства для преобразования двоично-десятичного кода в двоичный (1), содержащие регистры сдвига и памяти для преобразуемого двоично-десятичного кода и его выходного двоичного эквивалента, элементы «И» и узлы коррекции. Такие устройства содержат два многоразрядных, регистра, узлы коррекции по числу тетрад в преобразуемом двоично-десятичном коде, что усложняет устройство.

Наиболее близким по технической сущности решением задачи является преобразователь правильной двоично-десятичной дроби в двоичную (2), содержащий распределитель импульсов, регистр задержки, блок коррекции и блок выбора.

Схема такого преобразователя сложна.

Целью изобретения является упрощение устройства.

Эта цель достигается тем, что в предложен,ное устройство для преобразован|ия двоичнодесят ичного кода в двоичный введен тр иггер и регистр числа. Группа выходов регистра числа соединена с первой группой входов блока выбора, группа выходов иоторого соединена с группой входов блока коррекции, группа выходов которого соединена с регистром задержки, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами регистра числа, а четвертый выход регистра задержки соединен с четвертым входом регистра числа и с первым входом триггера, выход которого соединен с пятым входом регистра числа. Первый и второй выходы распределителя импульсов соединены соответственно с шестым и седьмым входами регистра числа, а третий с восьмым входом регистра числа и вторым входом триггера. Группа выходов и четверI5 тыи выход распределителя импульсов соединены соответственно со второй группой входов блока выбора и входом блока коррекции.

Группа входов регистра числа является группой входов устройства.

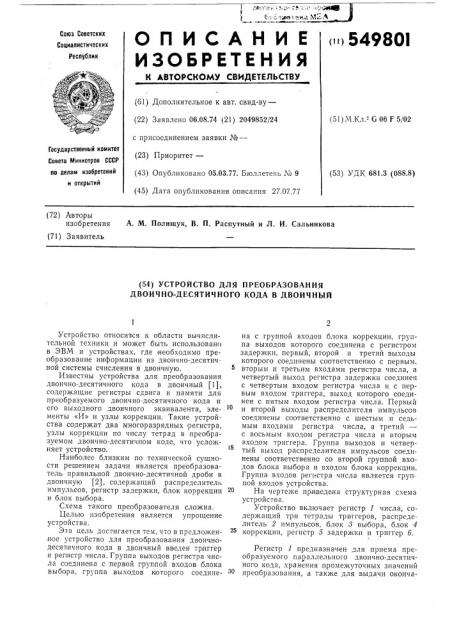

На чертеже приведена структурная схема устройства.

Устройство включает регистр 1 числа, содержащий три тетрады триггеров, распределитель 2 импульсов, блок 8 выбора, блок 4 коррекции, регистр 5 задержки и триггер 6.

Регистр 1 предназначен для приема преобразуемого параллельного двоично-десятичного кода, хранения промежуточных значений преобразования, а также для выдачи оконча549801

10

15 тельного результата преобразования в двоичном параллельном коде.

Распределитель 2 формирует импульсы, необходимые для синхронизации работы всех узлов устройства.

Блок 8 служит для поочередного пропускания содержимого тетрад на общий блок4 и выполнен в виде элементов И для разрядов каждой тетр ады.

Блок 4 предназначен для анализа и коррекции содержимого тетрад и представляет комбинационную схему, зависимость между входными и выходными сигналами которой такова, что входная комбинация кода, имеющая содержимое 8, 9, 10, 11 и 12 двоичных единиц, блоком 4 уменьшается на 8.

Регистр 5 предназначен для хранения четырехразрядной скорректированной информации до окончания такта коррекции данной тетрады.

Триггер б предназначен для временного хранения текущих значений четвертого разряда информации с выхода регистра 5.

Устройство работает следующим образом.

Двоично-десятичный код числа, предназначенного для преобразования в двоичный код, потетрадно располагается в регистре 1.

После этого содержимое всех тетрад поочередно, начиная с первой тетрады (элементы Т вЂ” T4), поступает через блок 8 на блок 4, где анализируются и при необходимости корректируются коды тетрад. С выхода блока 4 проанализированная информация тетрад поступает на регистр 5.

Четвертый разряд информации первой тетрады из регистра 5 поступает в триггер б для временного хранения, а первый, второй и третий разряды поступают в элементы

Т вЂ” Т4 первой тетрады регистра 1 соответственно. Информация второй тетрады, а затем третьей тепрады из регистра 5 поступает в регистр 1 со сдвигом относительно прежнего расположения на один разряд вправо. Содержимое тр иггера б поступает в элемент Т, третьей тетрады. После этого в регистре 1 располагаются в параллельном коде разряды двоичного числа, эквивалентного преобразуемому двоично-десятичному числу.

Состояния и выход триггера б соответствуют значениям двоичного последовательного кода.

Таким образом, устройство может быть использовано для преобразования двоично20

50 десятичного кода в параллельный и последовательный двоичный код.

Использование регистра числа для прием» преобразуемого двоично-десятичного числа, для хранения промежуточных значений преобразования, а также для выдачи окончательного результата преобразования позволило применить один блок коррекции для всех тетрад, тем самым упростить устройство и повысить его надежность.

Экономический эффект использования предлагаемого устройства возрастает с ростом числа разрядов преобразуемого числа.

Формула изобретения

Устройство для преобразования двоичнодесятичного кода в двоичный, содержащее распределитель импульсов, регистр задержки, блок коррекции и блок выбора, о тл и ч а ющ е е с я тем, что, с целью упрощения устройства, оно содержит трипгер и регистр числа, причем группа выходов регистра числа соединена с первой группой входов блока выбора, группа выходов которого соединена с группой входов блока коррекции, группа выходов которого соединена с регистром задержки, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами регистра числа, а четвертый выход регистра задержки соединен с четвертым входом регистра числа и с первым входом триггера, выход которого соединен с пятым входом регистра числа; пер вый и второй выходы распределителя импульсов соединены соответственно с шестым и седьмым входами регистра числа, а третий выход — с восьмым входом регистра числя и вторым входом триггера; группа выходов и четвертый выход распределителя импульсов соединены соответственно со второй группой входов блока выбора и входом блока коррекции; группа входов регистра числа является группой входов устройства.

Источники информации, принятые во внимание при экспертизе:

1, М. М. Сухомлинов и В. И. Выхованец

«Преобразователи кодов чисел», изд. «Техника», Киев, 1965, стр. 104, рис. 32.

2. Авторское свидетельство СССР № 404077, М, Кл. G 06 F от 07.10.71 г. (прототип).

Редактор Л, Утехина

Составитель Л. Сальникова

Техред М. Семенов

Корректор В. Гутман

Заказ 288,964 Изд. № 476 Тираж 899

ЦНИ!!ПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, уК-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент»

Подписное