Преобразователь параллельного двоичного кода в число- импульсный код

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

ОП ИСАН ИЕ

ИЗОБРЕТЕН ИЯ, <1>549802

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 19.11.74 (21) 2076710,24

/ (51) М.Кл. G 06 F 5/04 с присоединением заявки—

Гасударственный комитат (23) Приоритет— (43) Опубликовано 05.03.77. Бюллетень ¹ 9 (45) Дата опубликования описания 27.07,77

;Совета Министров СССР по делам изобретений и открытий (53) УДК 681.325 (088.8) (72) Автор изобретения

M. Л. Миневич (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО

ДВОИЧНОГО КОДА В ЧИСЛО-ИМПУЛЬСНЫЙ КОД

Изобретение относится к области автоматики и вычислительной техники и предназначено для преобразования параллельных двоичных кодов в число-импульсный код.

Известен преобразователь двоичного кода в последовательность импульсов (1).

Однако данный преобразователь содержит большое число различных элементов.

Наиболее близким техчическим решением к данному изобретению является преобразователь параллельного двоичного кода в чис.ло-импульсный код, содержащий регистр. счетчик, параллельные входы которого соединены с входными шинами, входами регистра и входами элемента ИЛИ, выход которого 15 соединен с входом элемента задержки, первый выход которого соединен с первым входом первого элемента И, выход которого соединен с одним из входов элемента ИЛИ и с выходной шиной, выход элемента ИЛИ со- 20 единен с нулевым входом триггера, и второй элемент И (2).

Недостаток этого преобразователя заключается в его сложности.

Целью изобретения является сокращение объема оборудования.

Эта цель достигается за счет того, что в предло>кенном устройстве счетчик выполнен в виде вычитающего счетчика, его выходы соединены с входами второго элемента И, ЗО один из входов которого соединен со вторым выходом элемента задержки, а выход с единичным входом триггера, выход которого соединен со вторым входом первого элемента И, выход которого соединен с последовательным входом счетчика.

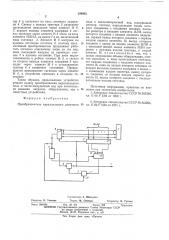

Блок-схема предлагаемого устройства представлена на чертеже.

Входные шины соединены с регистром 1, с параллельными входами каскадов счетчика

2 и со входами элемента ИЛИ 8, выход которого соединен со входом элемента задержки

4 и цепью установки «О» триггера 5.

Первый выход элемента задер>кки 4 через элемент И б соединен со входами вычитания счетчика 2, входом элемента ИЛИ 8 и с общим выходом устройства 7. Параллельные выходы счетчика 2 соединены со входами элемента И 8, дополнительный вход которого соединен со вторым выходом элемента задержки 4, а выход — с цепью установки «1» триггера 5.

Устройство работает следующим образом.

Двоичное число со входа поступает по параллельным шинам и регистр 1, в счетчик 2 и одновременно на вход элемента ИЛИ 8.

Если это число отлично от «О», т. е. содержится хотя бы в одном разряде «1», то на выходе элемента ИЛИ 8 появляется сигнал, который устанавливает в состояние «О» триг549802

Составитель А. Шкатулла

Техред М. Семенов

Редактор Л. Утехина

Корректор В. Гутман

Заказ 288/964 Изд. № 476 Тираж 899 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент> гер б и поступает на вход элемента задержки 4. Сигнал с выхода триггера б разрешает прохождение импульсов через элемент И б.

С первого выхода элемента задержки 4 сигнал проходит через элемент И б вновь на вход элемента ИЛИ 8, на выход 7 и на вычитающий вход счетчика 2. Элемент И 8 настроен на нулевое состояние счетчика 2, поэтому предлагаемый преобразователь продолжает работать согласно описанному выше до тех пор, пока последний импульс не переведет счетчик 2 в нулевое состояние. При этом подготавливается к работе элемент И 8, и сигнал со второго выхода элемента задержки 4 проходит через элемент И 8 и устанавливает триггер б в единичное состояние. Прекращается прохождение сигналов через элемент

И б, и устройство приходит в исходное состояние, Таким образом, предложенное устройство решает задачу преобразования параллельного кода в число-импульсный код при значительно меньших затратах оборудования, чем в известных устройствах.

Формула изобретения

Преобразователь параллельного двоичного кода в число-импульсный код, содержащий регистр, счетчик, параллельные входы которого соединены с входными шинами, входами регистра и входами элемента ИЛИ, выход, которого соединен с входом элемента задержки, первый выход которого соединен с первым входом первого элемента И, выход которого

10 соединен с одним из входов элемента ИЛИ и с выходной шиной, выход элемента ИЛИ соединен с нулевым входом триггера, и второй элемент И, отлич ающийся тем, что, с целью сокращения объема оборудования, счет15 чик выполнен в виде вычитающего счетчика, его выходы соединены с входами второго элемента И, один из входов которого соединен со вторым выходом элемента задержки а выход— с единичным входом триггера, выход которо20 го соединен со вторым входом первого элемента И, выход которого соединен с последовательным входом счетчика.

Источники информации, принятые во вни25 мание при экспертизе изобретения:

1. Авторское свидетельство СССР № 285346, кл. G 06 F 5/04 от 1969 г.

2. Авторское свидетельство СССР № 343264, 30 кл. G 06 F 5 04 от 1971 г.