Устройство для преобразования параллельного кода в последовательный

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

«»549804

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 10.01.75 (21) 20S5559,24 с присоединением заявки— (23) Приоритет (43) Опубликовано 05.03.77. Бюллетень ¹ 9 (45) Дата опубликования описания 27.07.77 (51) М.Кл. G 06 F 5/06

Государственный комитет

Совета Министров СССР по делам изобретений н открытий (53) УДК 681.325 (088.8) (72) Авторы изобретения

Ю. А. Авах и В. К. Фатин (71) Заявители (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ

ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ

Изобретение относится к области вычислительной техники, и может быть использовано для преобразования кода с заданием определенной циклограммы выдачи последовательных кодов и с многократным повторением каждого кода.

Известны устройства для преобразования кода (1), в которых осуществляется преобразование параллельного кода в последовательный путем последовательного опроса разрядов регистра, в который предварительно введено в параллельном коде слово, подлежащее преобразованию. Эти устройства для акратного повторения кода требуют примерно и-кратного увеличения количества элементов и становятся слишком громоздкими.

Наиболее близким техническим решением к данному изобретению является устройство для преобразования параллельного кода в последовательный, содержащее генератор импульсов, выход которого соединен с информационным входом первого счетчика, выходы которого соединены с дешифратором, первая группа выходов которого соединена с первой группой входов блока элементов И, вторая группа входов которого соединена с выходами регистра, информационные входы которого подключены к входным шинам, а управляющий вход соединен с первым выходом блока управления. Выходы блока элементов И соединены с входами первого элемента ИЛИ, выход которого подключен к выходной шине, элемент задержки (2).

Известное устройство не позволяет повтор5 но опрашивать одно и то же слово и формировать требуемые интервалы между словами.

Целью изобретения является расширение класса решаемых задач.

Эта цель достигается тем, что в предложенное устройство дополнительно введены второй счетчик, инвертор, элемент И и второй элемент

ИЛИ, первый вход которого соединен с вторым выходом блока управления, второй вход — с информационным входом второго счетчика и

15 первым выходом второй группы выходов дешифратора, второй выход той же группы соединен с входом блока управления, а третий выход второй группы выходов дешифратора соединен с первым входом элемента И, выход которого соединен с третьим входом второго элемента ИЛИ, выход которого через элемент задержки соединен с установочными входами первого и второго счетчиков. Выход второго счетчика через инвертор соединен с вторым входом элемента И.

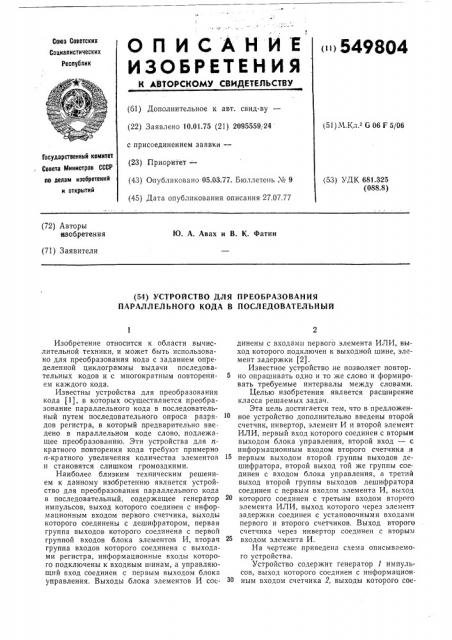

На чертеже приведена схема описыв".åìîro устройства.

Устройство содержит генератор 1 импульсов, выход которого соединен с информационным входом счетчика 2, выходы которого сое549804 динены с дешифратором 8. Первая группа выходов дешифратора 8 соединена с первой группой входов блока 4 элементов И, вторая группа входов которого соединена с выходами регистра 5, информационные входы которого подключены к входным шинам 61 — 6„а управляющий вход соединен с первым выходом блока 7 управления. Выходы блока 4 элементов И соединены с входами элемента ИЛИ

8, выход которого подключен к выходной шине 9. Первый вход элемента ИЛИ 10 соединен с вторым выходом блока 7 управления, второй вход — с информационным входом счетчика 11 и выходом 12 второй группы выходов дешифратора 8, выход 18 той же группы соединен с входом блока 7 управления, а выход 14 — с первым входом элемента И 15, выход которого соединен с третьим входом элемента ИЛИ 10. Выход элемента ИЛИ 10 через элемент 16 задержки соединен с установочными входами счетчиков 2 и 11. Выход счетчика 11 через инвертор 17 соединен со вторым входом элемента И 15.

Перед началом работы с блока 7 управления через элемент ИЛИ 10 на установочный вход счетчика 2 подается сигнал сброса, а на установочный вход счетчика 11 — сигнал установки в положение, соответствующее отсчету одной единицы. С другого выхода блока 7 на управляющий вход регистра подается сигнал, по которому в него записывается слово, подлежащее преобразованию из параллельного кода в последовательный.

Работа схемы начинается с отсчета числа импульсов, поступающих с генератора 1 импульсов на информационный вход счетчика 2.

С выхода счетчика 2 в параллельном коде на вход дешифратора 8 подается число отсчитанных импульсов. Когда это число дойдет до величины, соответствующей появлению сигнала на выходе 8, первой группы выходов дешифратора 8, первый логический элемент

И блока 4 элементов И пропускает информацию («нуль» или «единицу») из первого разряда регистра 5 на вход элемента ИЛИ 8.

Аналогично последовательно опрашиваются все разряды регистра 5, и информация с них в последовательном коде через элемент ИЛИ

8 поступает на выходную шину 9.

Через заданное время после опроса последнего разряда регистра появляется сигнал на выходе 14 второй группы выходов лешифратора 8 и, пройдя через элемент И 15, открытый сигналом с инвертора 17, элемен1

ИЛИ 10 и элемент 16 задержки, сбрасывает в «нуль» счетчик 2 и записывает вторую «единицу» в счетчик 11. Счетчик 2 снова начинаег отсчитывать импульсы, поступающие с генератора 1 импульсов, и последовательно опрг шивать разряды регистра 5.

По окончании второго цикла опроса снова появляется сигнал на выходе 14 дешифратора 8, и сбрасывается в нулевое состояни" счетчик 2, а счетчик 11 отсчитывает еще одну единицу.

I0

Зо

50 г

50 б5

После очередного цикла опроса регистра

5 счетчик 11 заполняется (его емкость равна требуемому числу повторений), на его выходе появляется потенциальный сигнал, который, пройдя через инвертор 17, снимает разрешающий сигнал со входа элемента И 15.

Поскольку счетчик 2 сбрасывается в нуль сигналом, переполнившим счетчик П, начинается новый цикл опроса регистра 5, но после его окончания сигнал с выхода 14 де шифратора 8 не проходит через элемент И

15 и счетчик 2 продолжает считать.

На блок 7 управления с выхода 18 дешифратора 8 поступает сигнал, по которому блок 7 управления дает команду в регистр 5 на сброс информации и запись нового слова.

Через заданный интервал времени появляется сигнал на выходе 12 дешифратора 8, который сбрасывает в нуль счетчик 11 и, пройдя через элемент ИЛИ 10 и элемент 16 задержки сбрасывает в «нуль» счетчик 2 и записывает «единицу» в счетчик 11. Начинается многократный опрос и передача в последовательном коде следующего слова.

Интервал времени между окончанием последнего опроса одного слова и началом опроса следующего слова задается соответству ющим выбором числа импульсов, определяющим появление сигнала на выходе 12 дешифратора.

Использование предлагаемого устройства обеспечивает по сравнению с известными устройствами следующие преимущества: п-кратное повторение каждого слова в последовательном коде и формирование требуемых интервалов времени между повторениями одного и того же слова и между различными словами достигается без существенного усложнения аппаратуры.

Формула изобретения

Устройство для преобразования параллельного кода в последовательный, содержащее генератор импульсов, выход которого соединен с информационным входом первого счетчика, выходы которого соединены с дешифратором, первая группа выходов которого соединена с первой группой входов блока элементов И, вторая группа входов которого соединена с выходами регистра, информационные входы которого подключены к входным шинам, а управляющий вход соединен с первым выходом блока управления, выходы блока элементов И соединены с входами первого элемента ИЛИ, выход которого подключен к выходной шине, элемент задержки, о т л ич а ю щ е е с я тем, что, с целью расширения класса решаемых задач, в него дополнительно введены второй счетчик, инвертор, элемент

И и второй элемент ИЛИ, первый вход которого соединен с вторым выходом блока управления, второй вход соединен с информационным входом второго счетчика и пер549804

Составитель В. Фатин

Техред М. Семенов

Корректор В. Гутман

Редактор Л. Утехина

Заказ 288,984 Изд. М 476 Тираж 899 Подпllëíñ

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, К-35, Раушскан наб., д. 4 5

Тип. Харьк. фил. пред. «Патент» вым выходом второй группы выходов дешифратора; второй выход той же группы соединен с входом блока управления, а третий выход второй группы выходов дешифратора соединен с первым входом элемента И, выход которого соединен с третьим входом второго элемента ИЛИ, выход которого через элемент задержки соединен с установочными входами первого и второго счетчиков; причем выход второго счетчика через инвертор соединен с вторым входом элемента И, Источники информации, принятые во вни8 мание при экспертизе изобретения:

1. СССР, а. с. Мв 265562, кл, G 06 F 5/OF) от 1968 г.

2. СССР, а. с. Кв 344575, кл. Н 03 К 5/01 от 1970 г.