Устройство для деления

Иллюстрации

Показать всеРеферат

()549808

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 16.05.75 (21) 2135423 24 с присоединением заявки— (23) Приоритет— (51) М.Кл. 6 06 F 7/50

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (43) Опубликовано 05.03.77. Бюллетень ¹ 9

Ф (45) Дата опубликования описания 27.07.77 (53) УДК 687.325 (088.8) (72) Авторы изобретения

В. И. Жабин, В. И. Корнейчук, В. П. Тарасенко и Г. И. Корниенко (71) Заявитель

Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалистической революции (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

1 — (В(1, 0(А(В

Изобретение относится к области вычислительной техники и может быть применено в

LIBM и специализированных цифровых вычислителях.

Известны устройства для деления, содержащие регистры операндов, сумматор и логические элементы (1). Операнды в этих устройствах могут быть представлены последовательным кодом.

Недостатком этих устройств является низкое быстродействие выполнения операции деления.

Наиболее близким техническим решением к предложенному изобретению является устройство, содержащее сумматор делимого, регистр делителя, подключенный через первый блок передачи кода к входам сумматора делимого, шины управления, первая из которых подключена ко входу сдвига сумматора делимого (2).

Недостатком этого устройства является небольшое быстродействие, равное 2п тактов.

Целью изобретения является повышение быстродействия.

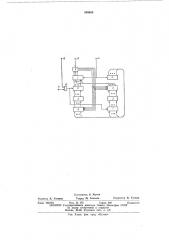

Эта цель достигается тем, что в предложенное устройство введены сумматор частного, три блока передачи кодов, регистр сдвига, ключ и элемент И. Вторая шина управленич подключена к входу регистра сдвига, выходы которого через второй и третий блоки передачи кодов подключены соответственно к входам регистра делителя и сумматора частного, выходы которого через четвертый блок передачи кодов подключены к соответствующим входам сумматора делимого. Выход трех старших разрядов сумматора делимого через ключ подключен к входу первого и третьего блоков передачи кодов.

10 Третья шина управления подключена к второму входу ключа, четвертая шина — к первому входу элемента И, к второму входу которого подключена информационная шина.

Выход элемента И подключен к входам вто15 рого и четвертого блоков передачи кодов.

На чертеже представлена схема устройства.

Оно содержит сумматор делимого 1, регистр делителя 2, сумматор частного З,,регистр сдвига 4, блоки 5 — 8 передачи кодов, ключ 9, элемент И 10 и шины управления 11—

14.

Устройство работает следующим образом.

На величины делимого А = а,а . 1а е... а„и делителя В =O,b,b р... Ь„накладывают следующие ограничения:

В исходном состоянии код делимого записан в и младших разрядах сумматора делимого 1 (два старших разряда сумматора 1 являются знаковыми), в старшем разряде регистра сдвига 4 записана единица, во всех разрядах регистра делителя 2 записаны единицы, а сумматор частного 8 установлен в нулевое состояние.

К началу каждого i-го цикла (i =1,2,..., n) вычислений на информационный вход 11 поступает инверсное значение Ь ; очередного

1О разряда делителя. При получении и старших разрядов частного (учитывается разряд с весом 2 ) устройство .работает в трехтактном режиме.

В каждом цикле вычислений на управляющие входы 12 — 14 поочередно поступают управляющие сигналы уь y>, y>. Управляющий сигнал у> поступает на вход элемента И 10, и если значение очередного разряда b дели20 теля равно нулю, сигнал с выхода элемента

И 10 осуществляет передачу кода из сумматора частного 8 в сумматор делимого 1 и из регистра 4 в регистр делителя 2. При этом код сумматора частного 8 прибавляется к коду сумматора делимого 1, а единица, записанная в -ом разряде регистра сдвига 4 устанавливает i-й разряд регистра делителя 2 в нулевое состояние (первым разрядом считается старший разряд). зо

По второму управляющему сигналу у> ключ

9 анализирует содержимое трех разрядов сумматора делимого 1, и в зависимости от их значений выдает единичный сигнал на один из четырех входов блоков 5 и 8 подачи кодов. При этом код из регистра делителя 2 передается в сумматор делимого 1, а код из регистра сдвига 4 — в сумматор частного 8. При передаче обратного и удвоенного обратного кодов в сумматоры 1 и 8 на свободные входь. 4О (например, для сумматора 1 — это входы, которые не связаны с выходами регистра 21 этих сумматоров подаются единичные сигналы.

По третьему управляющему сигналу уз осуществляется левый сдвиг на один разряд содержимого сумматора делимого 1 и правый сдвиг на один разряд содержимого регистра

4. При сдвиге отрицательных чисел в сумматоре 1 в младший разряд этого сумматора записывается единица. На этом заканчивается один цикл работы устройства.

После выполнения и циклов вычислений, т. е. после принятия на вход 11 всех и инверсных разрядов кода делителя, в и старших разрядах сумматора частного 8 оказывается сформированным код частного, имеющий стар ший разряд с весом 2 и и — 1 дробных разрядов. Если код частного должен иметь m) и разрядов, то, ля получения оставшихся m — n младших разрядов частного необходимо вы- б полнить дополнительно m — и циклов, Прп этом устройство работает в двухтактном ре:киме. Управляющие сигналы у и уз,поочередно подаются соответственно на входы 18 и 14.

При поступлении сигналов у и уз устройство работает так же, как было описано выше.

В этом режиме не осуществляется передача кода сумматора частного 8 в сумматор делимого 1 и передача кода из регистра сдвига

4 в регистр делителя 2, так как сигнал у, на управляющий вход 12 не поступает.

После выполнения дополнительных т — n циклов ги-разрядный код частного оказывается сформированным в сумматоре частного 8.

При получении дробных разрядов частного абсолютная погрешность результата не превышает в"личины 2 " ". Необходимую точность получения частного можно обеспечить правильным выбором разрядной сетки.

Таким образом, предложенное устройство обладает большим быстродействием выполнения операции деления по cpaBHeHHIO с известным в 2 раза.

Формула изобретения

Устройство для деления, содержащее сумматор делимого, регистр делителя, подключенный через первый блок передачи кодов ко входам сумматора делимого, шины управления, первая из которых подключена ко входу сдвига сумматора делимого, о т л и ч а ю щ е ес я тем, что, с целью повышения быстродействия, в устройство введены сумматор частного, три блока передачи кодов, регистр сдвига. ключ и элемент И; причем вторая шина управления подключена ко входу регистра сдвига, выходы которого через второй и третий блоки передачи кодов подключены соответственно ко входам регистра делителя и сумматора частного, выходы которого через четвертый блок передачи кодов подключены к соответствующим входам сумматора делимого; выход трех старших разрядов сумматора делимого через ключ подключен ко входу первого и третьего блоков передачи кодов, третья шина управления подключена ко второму входу ключа, четвертая шина — к первому входу элемента И, ко второму входу которого подключена информационная шина; выход элемента

И подключен ко входам второго и четвертого блоков передачи кодов.

Источники информации, принятые во внимание при экспертизе:

1. СССР а. с. 396689, кл. G 06 F 7/39 от

1971 г.

2. К. 1. Some Electronic Logic Circuits for

Serial — Parallel arithmetic. The Кайо an

Electronic Fngineer № 2, 1969, стр. 96, рис. 5.

549808

ro а

Составитель В. Жуков

Техред М. Семенов

Корректор В. Гутман

Редактор Л. Утехина

Тип. Харьк, фил. пред, «Патент»

Заказ 288/964 Изд. № 476 Тираж 899 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5