Анатоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

OllH

ИЗОБ

>549837

Соии Советских

Социалистических

Реслублии

К АВТОРСКО (б1) Дополнительн (22) Заявлено 19.0 с присоединением з (23) Приоритет— (43) Опубликовано (45) Дата опублик (51)М.Кл.е 6 11 С 27/00

Гссударстсеииь.й комитет

Совета Иииистров СССР по делам изобретеиий и открытий (53) УДК 681.327.66 (088.8) (72) Автор изобретения

Ю. В. Каштанов (71) 3 аявитель (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к устройствам вычислительной техники и может быть использовано для запоминания, хранения и считывания аналоговой информации.

Известны аналоговые запомпнаюшие устройства, содержащие интегратор, компаратор, ключи и логические элементы.

В качестве такого устройства может быть рассмотрен преобразователь напряжения в интервал времени (1), если в качестве входного использовать напряжение, равное по величине и противоположное по знаку опорному напряжению, а в качестве опорного интервала времени — входной запоминаемый. Однако такое устройство не позволяет осуществлять повторное считывание записанной информации.

Наиболее близким по технической сущности и достигаемому результату к изобретению является устройство, содержащее интегратор, вход которого через первый ключ подсоединен к шине постоянного напряжения, выход интегратора соединен со входом второго ключа, управляющий вход которого подключен к шине записи, компаратор, один из входов которого соединен с выходом ячейки памяти, шину входного сигнала и шину считывания (2). Однако такое устройство довольно сложно и вследствие этого недостаточно надежное.

Кроме того, оно не позволяет осуществлять запоминание сигналов, представленных интервалом времени.

Цель изобретения — повышение надежности устройства.

5 Поставленная цель достигается тем, что в устройство дополнительно введены элементы

И и ИЛИ, один вход элемента ИЛИ подключен к шине входного сигнала, другой его вход соединен с шиной считывания и с одним из

10 входов элемента И, выход элемента ИЛ1Л соединен с управляющим входом первого ключа, другой вход элемента И подключен к выходу компаратора, другой вход которого соединен с выходом интегратора, вход ячейки памяти соединен с выходом второго ключа, выход элемента И соединен с выходом устройства.

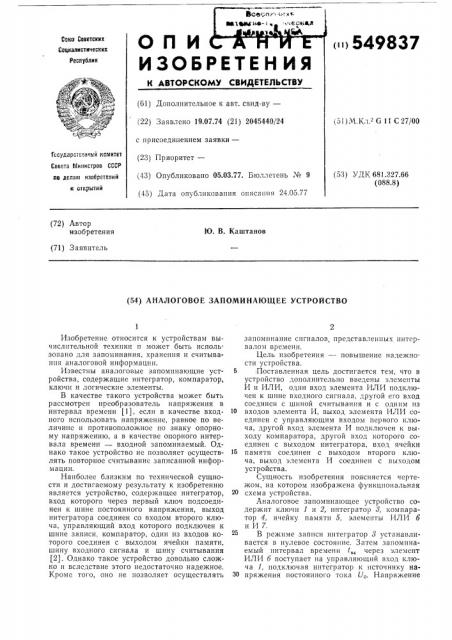

Сущность изобретения поясняется чертежом, на котором изображена функциональная

20 схема устройства.

Аналоговое запоминающее устройство содержит ключи 1 и 2, интегратор 8, компаратор 1, ячейку памяти 5, элементы 1ЛЛИ б и И 7.

В режиме записи интегратор 8 устанавливается в нулевое состояние. Затем запоминаемый интервал времени „,. через элемент

ИЛИ б поступает на управляющий вход ключа 1, подключая интегратор к источнику наЗ0 пряжения постоянного тока (1с. Напряжение

549837 (/ з = и ./О в х (1)

40 вых / вх i

Юх на выходе интегратора 8 линейно возрастает и в конце /„х достигает значения где

ʄ— коэффициент передачи интегратора 8.

Управляющим импульсом записи замыкается ключ 2, подключающий выход интегратора 8 ко входу ячейки памяти 5, которая запоминает выходное напряжение.

В режиме хранения оба ключа разомкнуты, а ячейка памяти 5 хранит полученное напряжение.

В режиме считывания записанной информации управляющим импульсом сброса интегратор 8 вновь устанавливается в нулевое состояние. Затем управляющим импульсом считывания через элемент ИЛИ б замыкается ключ 1, вторично подключая сигнальный вход интегратора 8 к источнику напряжения постоянного тока Uo. Выходное напряжение интегратора 8 линейно возрастает и в момент от начала импульса считывания достигает значения, равного выходному напряжению 2Б ячейки памяти 5. Компаратор 4 меняет свое состояние, прекращая выдачу управляющего импульса считывания через элемент И 7 на выход устройства.

Для этого момента можно записать, что З0

U„,= К„. U„ t,„„. =- U,„=R„U, t„., (2) где:

U„, — выходное напряжение интегратора 8 в з режиме считывания;

U„„— выходное напряжение ячейки памяти 5.

Отсюда следует, что т. е. считываемый выходной интервал времени равен входному записанному.

При считывании напряжение, запомненное 4 ячейкой памяти 5, не уничтожается. Следовательно, режим считывания может осуществляться многократно.

Сравнительный анализ схем и возможностей данного аналогового запоминаюгцего устройства и известного показывает, что число элементов схемы может быть уменьшено не менее, чем на 20%, а следовательно, в такой же мере может быть увеличена надежность. Данное устройство в отличие от известного позволяет производить запоминание и воспроизведение не только сигналов, представленных напряжением постоянного тока, но и сигналов, представленных интервалом времени.

Формула изобретения

Аналоговое запоминающее устройство, содержащее интегратор, вход которого через первый ключ подсоединен к шине постоянного напряжения, выход интегратора соединен со входом второго ключа, управляющий вход которого подключен к шине записи, компаратор, один из входов которого соединен с выходом ячейки памяти, шину входного сигнала и шину считывания, о тл и ч а ю ще е с я тем, что, с целью повышения надежности устройства, в него введены элементы И и ИЛИ, один вход элемента ИЛИ подключен к шине входного сигнала, другой его вход соединен с шиной считывания и с одним из входов элемента И, выход элемента ИЛИ соединен с управляющим входом первого ключа, другой вход элемента И подключен к выходу компаратора, другой вход которого соединен с выходом интегратора, вход ячейки памяти соединен с выходом второго ключа, выход элемента И соединен с выходом устройства.

Источники информации, принятые во внимание при экспертизе:

1. Смолов В. Б. и др. Полупроводниковые кодирующие и декодирующие преобразователи, Л., «Энергия», 1967 r.

2. Авторское свидетельство СССР № 394855, кл. G 27/00 от 22.08.73 r.

549837 г

1 Риг 2

Составитель А. Воронин

Редактор И. Тимофеева Техред И. Сметанина Корректор И. Симкина

Заказ 277/957 Изд. № 470 Тираж 769 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )K-35, Раушская наб., д. 4/5

Тип. Харьк. фнл. пред. «Патент»