Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистицеских

Республик (11) 549876 (61) Дополнительное к авт. свид-ву— (22) Заявлено 13.06.75 (21) 2143628/09 с присоединением заявки № (23) Приоритет— (43) Опубликовано05.03.77. Бюллетень № 9 (45) Дата опубликования описания 20.05.77 (51) и. Кл

Н 03 Р 3/45

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) У ДК 62 I. 375. .024 (088.8) (72) Авторы изобретения

Г. В. Гаврилов, М. X. Риитсаар и P. Э. Суль (71) Заявитель (54) ДИФФЕРЕН11ИАЛЬНЫЙ УСИЛИТЕЛЬ

Изобретение относится к радиотехнике.

Известен дифференциальный усилитель на транзисторах, включенных по схеме с общим эмиттером, между коллекторами которых включен резистивный делитель. а эмиттеры через общий генератор тока соединены с первой шиной источника питания fl), Однако известный усилитель не обеспечивает хорошего подавления синфазного сигнала. )О

Цель изобретения — улучшение подавления синфазного сигнала.

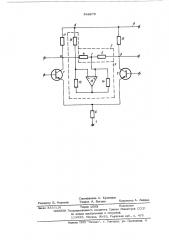

Для этого в дифференциальном усилителе на транзисторах, включенных по схеме с общим эмиттером, между коллекторами ко- 15 торых включен резистивный делитель, а эмиттеры через общий генератор тока соединены с первой шиной источника питания, между отводом делителя и второй шиной источника питания включен элемент с отрицатель- 20 ным сопротивлением, выполненный на операционном усилителе, между входами и выходом которого включены резисторы; при этом к отводу делителя подключен неинвертируюший вход операционного усилителя, а ко 25 второй шине источника питания — неинвертирующий вход, На чертеже приведена принципиальная электрическая схема дифференциального усилителя.

Между коллекторами транзисторов 1 и

2, включенных по схеме с общим эмиттером, включен делитель 3, состоящий из резисторов 4 и 5, а эмиттеры через общий генератор тока 6 соединены с первой шиной 7 источника питания, причем между отводом делителя 3 и второй шиной 8 источника питания включены элемент с отрицательным сопротивлением 9, а также резисторы 10 и 11. Элемент с отрицательным сопротивлением 9 выполнен на операционном усилителе 12, между входами и выходом которого включены резисторы 13 и 14; при этом к отводу делителя 3 подключен неинвертирующий вход усилителя 12, а ко второй шине 8 источника питания через резистор 15— инвертирующий вход.

Дифференциальный усилитель работает следующим о(разом.

549876

В сбалансированном дифференциальном усилителе синфазный входной сигнал приводит к изменению только уровня синфазного напряжения в точках О и Ъ . Парафазное напряжение в этих точках в этом случае отсутствует. Напряжение в точке С равно полному значению синфазного выходного сигнала. При этом дифференциальный усилитель можно рассматривать как два параллельно включенных транзистора 1 и 2 с общим резистором в цепях коллекторов. Эквивалентное значение сопротивления К резистора в цепях коллекторов транзисторов 1 и 2 определяется выражением R„(R2+ 2КЭ) я л

К4 — сопротивление генератора тока 6;

А — коэффициент, зависящий от от- 35 ношений между сопротивлениями резисторов в эмиттерных и коллекторных цепях транзисторов 1 и 2, а также параметров этих транзисторов. 40 где

При условии R =-Я /2, Я =} .} и }(=p, Для парафазного выходного сигнала, действующего в точках O b точка С является узлом с нулевым потенциалом.

R4 — сопротивление резисторов 10 и 11; — сопротивление резисторов 4

2 и 5; — сопротивление элемента с отри5 цательным сопротивлением 9 относительно точек С и

Коэффициент усиления К дифференциального усилителя для синфазного сигнала определяется отношением

ЯЭ4

Эл

224

З0

Эквивалентное значение сопротивления резистора в коллекторе транзистора 1

Э2 или 2 для парафазного выходного сигнала определяется отношением л 4

Э2 }}, р ° л

При Я„ R, э2- } „.

Таким образом, элемент с отрицательным сопротивлением 9, не влияя на усиление парафазного входного сигнала в дифференциальном усилителе, в то же время эффективно подавляет синфазный выходной сигнал на выходе дифференциального усилителя.

Формула изобретения

1. Дифференциальный усилитель на транзисторах, включенных по схеме с общим эмиттером, между коллекторами которых включен резистивный делитель, а эмиттеры через общий генератор тока соединены с первой шиной источника питания, о т л и ч а юш и и с я тем, что, с целью улучшения подавления синфазного сигнала, между отводом делителя и второй шиной источника питания включен элемент с отрицательным сопротивлением.

2. Дифференциальный усилитель по и. 1, о т л и ч а ю ш и и с я тем, что элемент с отрицательным сопротивлением выполнен на операционном усилителе, между входами и выходом которого включены резисторы, при этом к отводу резистивного делителя подключен неинвертируюший вход операционного усилителя, а ко второй шине источника питания — инвертируюший вход.

Источники информации, принятые во внимание нри экспертизе изобретения:

1. Таков Т. и др. Линейни интегрални схеми, София, "Техника", 1974, с. 162, рис. 6.17.

549876

Составитель А. Кузнецов

Техред А. Богдан Корректор А. Лакида

Редактор Б. Федотов

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 335/116 Тираж 1052 Подписное

ПНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5