Компенсационный стабилизатор напряжения постоянного тока

Иллюстрации

Показать всеРеферат

xffч9еcyщт

> б ч:-потека ggp, Оп ИСАНИ Е

ИЗОБРЕТЕ Н ИЯ 55062б

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 04.06.73 (21) 1927659/07 с присоединением заявки №вЂ” (23) Приоритет—

Оиуоликовано 15.03.77. Бюллетень № 10

Дата опубликования описания 03.05.77 (51) Ч. Кл.- G 05F 1i56

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.316.722.1 (088.6) (72) Автор изобретения

H. В. Селиванов

Киевский ордена Ленина политехнический институт имени 50-летия

Великой Октябрьской социалистической революции (71) Заявитель

154) КОМ П Е Н САЦ И О Н Н Ы Й СТАБИЛИЗАТОР НА П РЯ)КЕ Н И Я

ПОСТОЯННОГО ТОКА

Изобретение относится к области радиоэлектроники, а именно к стабилизаторам постоянного напряжения, выполненным на гибридно-пленочных схемах, где важны малые габариты, вес, а также простое схематическое решение отдельных микросхем, входящих в устройство.

Известен компенсационный стабилизатор напряжения постоянного тока, содержащий последовательный регулирующий транзистор и цепь обратной связи (1). В таком стабилизаторе для уменьшения мощности рассеивания ггараллельно переходу коллектор — эмиттер регулирующего транзистора включен резистор — шунт. Недостатком известного стабилизатора является зависимость коэффициента стабилизации от тока нагрузки.

Наиболее близким к изобретению по технической сущности является компенсационный стабилизатор напряжения постоянного тока, содержащий последовательный регулирующий транзистор, коллектор которого соединенсодпим из входных выводов для подключения питающей сети, эмиттер через буферный блок связан с одним из выходных выводов для подключения нагрузки, а база подключена к выходу транзисторного усилителя цепи обратной связи с источником опорного напряжения па одном пз входов и измерительным органом на другом входе 12).

Принцип действия стабилизатора с буферным блоком основан на том, что при малых токах нагрузки или увеличении входного напряжения сети роль регулирующего транзи5 стора выполняет буферный транзистор. При увеличении тока нагрузки илп уменьшении входного напряжения сети напряжение на переходе коллектор — база буферного транзистора 1 меньшается, TBI< как B коллекторпой

10 цепи включен шунтовой резистор.

При дальнейшем увеличении тока нагруз;ки до максимального .значения и мгснимальном напряжении сети напряжение на переходе коллектор — база становится равным ну15 лю, а затем меняет знак, т. е. рабочая точка буферного транзистора переходит из линейной области в область насыщения. Вследствие этого мощность рассеивания буферного транзистора значительно уменьшается и боль20 шая часть ее рассеивается на шунтовом резисторе, который имеет большую допустимую температуру и меньшие габариты.

Однако для обеспечения минимальной мощности рассеивания на буферном транзп25 сторе необходимо величину поминала Шунтового резистора выбрать как можно большей.

Это приводит к повышению напряжения на переходе коллектор — эмиттер регулирующего транзистора и увеличению мощности рассеи30 вания на последнем, Кроме того, при перехо550626

3 де буферного транзистора из линейной области в область насыщения его коэффициент усиления по току резко падает, что приводит к ухудшению качественных показателей стабилизатора.

Для улучшения весогабаритных характеристик и уменьшения мощности рассеивания иа регулирующем транзисторе в предлагаемом стабилизаторе буферный блок состоит по крайней мере из двух каскадов, каждый из которых выполнен по схеме составного транзистора, состоящего из основного и по крайней мере двух согласуюгцих транзисторов, причем коллектор каждого из основных транзисторов через последовательную цепочку из двух резисторов соединен с коллектором регулирующего транзистора, эмиттер — с одним из выходных выводов для подключения нагрузки, коллектор каждого из первых согласующих транзисторов через резистор подключен к точке соединения резисторов соответствующей последовательной цепочки, а эмиттер регулирующего транзистора соединен с базами вторых согласующих транзисторов.

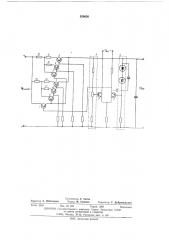

На чертеже дана принципиальная электрическая схема описываемого стабилизатора.

Коллектор последовательного регулирующего транзистора 1 стабилизатора соединен с одним из входных выводов для подключения питающей сети, эмиттер через буферный блок связан с одним из выходных выводов для подключения нагрузки, а база подключена к выходу усилителя цепи обратной связи на транзисторах 2 и 3 с источником 4 опорного напряжения иа одном из входов и измерительным органом 5 иа другом входе. Буферный блок состоит по крайней мере из двух каскадов, каждый из которых выполнен по схеме составных транзисторов, состоящих из основных 6 и 7 и двух согласующих 8, 9 и

10, 11 транзисторов. Коллектор, каждого основного транзистора через последовательную цепочку из резисторов 12, 13 и 14, 15 соединен с коллектором регулирующего транзистора 1, Кроме того, коллекторы согласующих транзисторов 8 и 10 через резисторы 16 и 17 подключены к точке соединения резисторов соответствующей последовательной цепочки.

При таком выполнении схемы иа основном регулирующем транзисторе 1 при максимальном токе нагрузки рассеивается незначительная мощность (определяемая необходимым током для поддержания регулирующего транзистора в линейном режиме) и снижается требование по напряжению к регулирующему транзистору, Это достигается увеличением чисГ) !

О

-(5

50 иЗ

4 ла управляемых буферных блоков, что позволяет уменьшить суммарную величину сопротивления резисторов шуита, так как управляемые буферные блоки включены параллельно регулирующему транзистору. Кроме того, включение транзисторов 6 и 7 при соответствующем условии выбора величины обратной связи при помощи резисторов 12 и 16 или 14 и 17 позволяет поддерживать коэффициент усиления по току практически постоянным в диапазоне расчетного тока нагрузки при минимальной мощности рассеивания на транзисторах 1, 6 и 7, что обеспечивает высокие качественные параметры стабилизатора.

Формула изобретения

Компенсационный стабилизатор напряжения постоянного тока, содержащий последовательный регулирующий транзистор, коллектор которого соединен с одним из входных выводов для подключения питающей сети, эмиттер через буферный блок связан с одним из выходных выводов для подключения нагрузки, а база подключена к выходу транзисторного усилителя цепи обратной связи с источником опорного напряжения на одном из входов и измерительным органом на другом входе, отл и ч а ю шийся тем, что, с целью улучшения весогабаритных характеристик и уменьшения мощности рассеивания на регулирующем транзисторе, буферный блок состоит по крайней мере из двух каскадов, каждый из которых выполнен по схеме составного транзистора, состоящего из основного и по крайней мере двух согласующих транзисторов, причем коллектор каждого из основных транзисторов через последовательную цепочку из двух резисторов соединен с коллектором регулиру(ощего транзистора, эмиттер — с одним из выходных выводов для подключения нагрузки, коллектор каждого из первых согласующих транзисторов через резистор подключен к точке соединения резисторов соответствующей последовательной цепочки, а эмиттер регулирующего транзистора соединен с базами вторых согласующих транзисторов.

Источники информации, принятые во внимание при экспертизе:

1. Карпов В. И. «Полупроводниковые компенсационные стабилизаторы напряжения и тока», М., «Энергия», 1967, с. 56, рис. 37б.

2. Карпов В. И. «Полупроводниковые компенсационные стабилизаторы напряжения и тока», М., «Энергия», 1967, с. 56, рис. 37а (прототип) .

550626

Составитель С. Ситко

Редактор А. Пейсоченко Техред М. Семенов 1(орректор T. Добровольская

Заказ 2538 Изд, № 27 9 Тираж 1О69 Подписное

ЦНИИПИ Государсгвенного комитета Совета Министров СССР о делам изобретений и открьгвий

113035. Москва, Ж-35, Раушская наб., д. 4/5

МОТ, Загорский филиал