Устройство для преобразования двоичнодесятичных чисел в двоичные

Иллюстрации

Показать всеРеферат

Вф внв

" . " " Ф з ®ск-., Ю

О П И С А Н И т1ц 550633

ИЗОБРЕТЕН И

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕДЬС (61) Дополнительное к авт. свид-ву (22) Заявлено 03.10.75 (21) 2177815/24 с присоединением заявки Кз (23) Приоритет

Опубликовано 15.03.77. Бюллетень Ме 1

Дата опубликования описания 13.04.7i7 (51) М. Кл С 06F 5/02

Государственный комитет, Совета Министров СССР по делам изобретений н открытий

1 (53) УДК„681.32,53 (088.8) (72) Авторы изобретения

И, И. Гут, Р, Б. Дунец, И. Л. Колодчак и В. К. Овсяк (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ

ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ В ДВОИЧНЫЕ

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных машинах и системах автоматического управления.

Известны устройства для преобразования двоично-десятичных чисел в двоичные, реализующие формулу Горнера и содержащие регистры, сумматоры и устройства для умножения на 10 путем сдвига на один и три разряда с последующим суммированием 11).

Недостатком этих устройств является большое количество используемой аппаратуры.

Наиболее близким техническим решением к данному изобретению является устройство для преобразования двоично-десятичных чисел в двоичные, содержащее динамический регистр, последовательный сумматор, выход которого соединен со входом динамического регистра, и регистр тетрады (2). Однако такое устройство имеет сравнительно низкое быстродействие.

С целью повышения быстродействия предлагаемое устройство содержит шину сигналов управления и три элемента И, выходы которых соединены с соответствующими входами последовательного сумматора, первые входы элементов И соединены соответственно с выходами первого, второго и четвертого разрядов регистра тетрады, а вторые входы соединены с шиной сигналов управления, вход четвертого разряда регистра тетрады соединен с выходом динамического регистра.

Это позволяет практически в два раза повысить быстродействие за счет совмещения во времени операций сложения и уменьшения на 10.

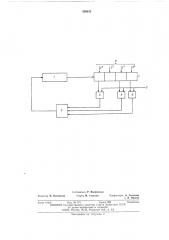

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит динамический регистр

1, выход которого соединен со входом четвертого разряда регистра 2 тетрады, а вход — с выходом последовательного сумматора 3, входы которого подключены к выходам элементов

И 4 — 6, причем одни входы элементов И соединены с выходами четвертого, второго и первого разрядов регистра 2 тетрады соответственно, а другие входы элементов И вЂ” с шиной 7 сигналов управления. Код тетрады поступает на входы 8 регистра 2 тетрады.

В исходном состоянии динамический регистр

1 и регистр 2 тетрады установлены в нуль.

Элемент И 6 открыт, а элементы 4, 5 закрыты сигналами по шине 7. Старший разряд преобразуемого числа в двоично-десятичном коде поступает в регистр 2 тетрады параллельным кодом. B первом такте код младшего (первого) разряда регистра 2 тетрады через открытый элемент И 6 поступает на вход последовательного сумматора 3, сигнал с выхода ко3 торого поступает на вход динамического ре550633 гистра 1. Далее происходит сдвиг на один разряд вправо хранящейся информации в динамическом регистре 1 и в регистре 2 тетрады. При этом выходной сигнал последовательного сумматора 3 заносится в динамический регистр 1, а сигнал с выхода динамического регистра 1 запоминается в освобожденном от информации четвертом разряде регистра

2 тетрады на один такт, что эквивалентно умножению числа на два. Во втором такте преобразования сигналом, поступающим по шине

7, элемент И 4 открывается, на входы последовательного сумматора 3 поступают через открытый элемент И б код очередного разряда тетрады преобразуемого числа и через открытый элемент И 4 — код с выхода четвертого разряда регистра 2 тетрады, в котором хранится результат умножения числа на два.

Сумма, образованная в результате сложения, с выхода последовательного сумматора 3 поступает на вход динамического регистра 1.

Происходит второй сдвиг вправо на один разряд информации регистра 1 и 2. Третий такт работы устройства аналогичен второму. В четвертом такте сигналом, поступающим по шине 7, открывается элемент И 5. При этом на входы последовательного сумматора 3 с регистра 2 тетрады поступают: код с выхода четвертого разряда через элемент И 4 (результат умножения числа на два), код с выхода второго разряда через элемент И 5 (результат умножения числа на восемь) и код очередного (старшего) разряда тетрады преобразуемого числа через элемент И б. Происходит четвертый сдвиг вправо.

В пятом и во всех последующих тактах, обшее число которых равно числу разрядов преобразованного числа, сигналом по шине 7 элемент И 6 закрывается и на последовательный сумматор 3 поступают коды с выходов регистра 2 тетрады через элементы И 4, 5 и происходит в каждом такте сдвиг информации в регистрах 1 и 2 на один разряд вправо.

Вследствие этого в динамическом регистре 1 оказывается число равное А 10+А ь где

А — разряды двоично-десятичного числа.

В следующем цикле в регистр 2 тетрады поступает очередная тетрада преобразуемого числа и работа устройства повторяется аналогично первому циклу. Процесс преобразования заканчивается прибавлением младшего разряда десятичного числа к содержимому динамического регистра 1, умноженному на десять.

Результат преобразования хранится в регистре 1.

Предлагаемое изобретение уменьшает время преобразования за счет того, что процессы умножения кода динамического регистра 1 на десять и сложения этого кода с кодом очередной тетрады преобразуемого числа совмещены во времени и выполняются в одном и том же цикле. Время преобразования Т определяется как:

15 где t — длительность одного цикла; и — количество разрядов двоично-десятичного числа.

При равных длительностях циклов по сравнению с известными аналогичными преобразователями предлагаемое устройство имеет в

2и — 1 раз выше быстродействие. и

Формула изобретения

Устройство для преобразования двоичнодесятичных чисел в двоичные, содержащее ди30 намический регистр, последовательный сумматор, выход которого соединен со входом динамического регистра, и регистр тетрады, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит шину сигналов

35 управления и три элемента И, выходы которых соединены с соответствующими входами последовательного сумматора, первые входы элементов И соединены соответственно с выходами первого, второго и четвертого разрядов регистра тетрады, а вторые входы соединены с шиной сигналов управления, вход четвертого разряда регистра тетрады соединен с выходом динамического регистра.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 269598

М, кл. G 06 F 5/02, опубл. 1968 г.

2. Авторское свидетельство СССР № 329525

5Э М. кл. G 06F 5/02, опубл. 1970 r.

Редактор Н. Каменская

Составитель P. Яворовская

Техред М. Семенов

Корректоры: А. Галахова и Л. Орлова

Заказ 612i8 Изд. № 271 Тираж 899 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, )К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2