Цифровой экстраполирующий преобразователь

Иллюстрации

Показать всеРеферат

ОП И HE

ИЗОБРЕТЕНИЯ нц 550641

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 08.05.75 (21) 2131638/24 с присоединением заявки № (23) Приоритет

Опубликовано 15.03.77. Бюллетень № 10

Дата опубликования описания 15.04.77 (51) М. Кл з G О6Г 15/20.б 05В 19/18

Государственный комитет

Совета Министров СССР по делам изобретений

И 0TKPblThN (53) УДК 621-503.55 (088.8) (72) Авторы изобретения

H. А, Сарычев, М. Б. Никифоров и А. Ф. Соколов

Рязанский радиотехнический институт (71) Заявитель (54) ЦИФРОВОЙ ЗКСТРАПОЛИРУ1О1ЦИЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах автоматизированного управления объектами.

Известен цифровой экстраполирующий преобразователь, содерхкащий первый регистр памяти, входы которого соединены с шинами входного кода, а выходы — с соответствующими входами преобразователя «код — частота»", .второй регистр памяти, реверсивный счетчик, элементы И, блок прогноза и линейный интерполятор (1).

Недостаток такого преобразователя — большие затраты оборудования на блок прогноза и линейный интерполятор.

Наиболее близким техническим решением к данному изобретению является цифровой экстраполятор, содержащий первый регистр, входы которого соединены с установочными входами реверсивного счетчика и с кодовым входом преобразователя, а выходы — со входом первого преобразователя «код — частота» и через последовательно соединенные первый элемент И, второй регистр, подключенный ко второму преобразователю «код — частота», второй элемент И третий регистр — со входами третьего преобразователя «код — частота», причем управляющие входы первого и второго элементов И подключены к тактовому входу преобразователя (2).

Недостатком этого экстраполятора является ограниченная точность воспроизведения кривых выше первого порядка, перерегулирование при скачках входного сигнала, т. е. низкая

5 точность преобразователя.

С целью повышения точности в предлагаемый преобразователь введены четыре триггера, первый вычислительный блок, блок синхронизации и последовательно соединенные сум10 мирующий счетчик, четвертый преобразователь «код — частота», блок коммутации, второй вычислительный блок, входы которого подключены к выходу второго преобразователь «код — частота» и единичным вы15 ходам первого, второго н третьего триггеров, а выходы через блок синхронизации — ко входам реверсивного счетчика, третий вычислительный блок, пятый триггер, третий элемент И, управляющий вход ко20 торого подключен к тактовому входу преобразователя и входу установки в нуль суммирующего счетчика, и шестой триггер, единичный выход которого подключен к нулевому входу пятого триггера, счетные входы второго и чет25 вертого триггеров подсоединены к выходам соответственно первого и третьего преобразователей «код — частота», единичные выходы этих триггеров, подключенные к счетным входам первого и третьего триггеров соответст30 венно, н выход второго преобразователя

550641

«код — частота» соединены через первый вычислительный блок со входами блока коммутации и четвертого преобразователя «код— частота», причем единичный выход пятого триггера подключен к запрещающему входу блока синхронизации.

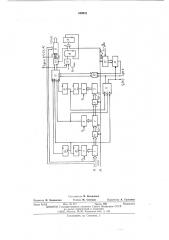

На чертеже показана схема предлагаемого преобразователя.

Он содержит регистры 1 — 3, элементы И

4 — б, преобразователи «код — частота» 7 — 10, вычислительные блоки 11 — 13, триггеры 14—

19, блок синхронизации 20, реверсивный счетчик 21, суммирующий счетчик 22, блок коммутации 23, тактовый 24 и кодовый 25 входы преобразователя.

Цифровой экстраполирующий преобразователь работает следующим образом.

По тактовому импульсу, совпадающему во времени с моментами поступления нового значения кода, открываются элементы И 4 и 5 и происходит перепись содержимого регистра в регистр 3, регистра 2 — в регистр 3, новое значение кода записывается в регистр 1. Таким образом в регистрах 1, 2 и 3 хранятся значения N„, N < и N > соответственно. Преобразователи 7, 8 и 9 преобразуют эти коды в частотно-импульсные сигналы. Триггеры 14, 15, 16, 17 предназначены для обеспечения необходимых весовых коэффициентов. Частоты с выхода триггера 15, преобразователя «код— частота» 8 и триггера 17 с весами 0,5, 1, 0,5 соответственно подаются на первый вычислительный блок 11, на выходе которого формируется частота, пропорциональная второй производной, и знак второй производной. На вход

Й вЂ” разрядного счетчика 22, который обнуляется каждым TBKTOBbIivl импульсом, подается

2( частота F, = —, в результате чего в счетТ чике в каждом интервале Т формируется линейно нарастающий код

NÄ gz) =,",; О а <.т, g1, 2) который подается на преобразователь «код— частота» 10. В качестве опорной частоты на преобразователь 10 подается частота F,", пропорциональная второй производной, вследствие чего выходная частота этого преобразователя

F,„„, (n, a) = F" fn, а) (сч И, о) )0,5N(n) — N(n — 1)+0,5N(n — 2)I a, (3) где m — разрядность регистров 1, 2, 3, Fo — опорная частота преобразователей 7, 8, 9, t

o= —.

Т

Блок коммутации 23 подает F»« „ на положительный или отрицательный входы второго вычислительного блока 12, на который с триггеров 14, 15, 16 и с преобразователя «код частота» 8 подаются частоты с коэффициентами 0,25, 0,5, 0,25, 1 соответственно.

В результате этого на выходе вычислительного блока 12 формируется частота

F (3

F (n,a)= 1 — N(n) — N(и — 1)+

+ — N (и — 2) + — — а — N (и) — N (n — 11+

1 F,т

4 2,2

10 1

+ — N(n — 2J )I (4) и ее знак з1 пЕ

Частотно-импульсный сигнал F., интегрируется реверсивным счетчиком 21, в результате чего код в нем ж„(,.1 =Л ()+ „, ° (— N(n) — N(n — 1)+20

+ у (n 2) + о у (n) о — Л((и — 1) + — Ф (и — 2) (.

2 (5) 25

Нр» выполнении условия гт гт

2m+ 2( выражение (5) приводится к виду

NÄ(n, а1= Л((n1+ (—,N)n) — 2N (и — 1) +

+ — N (n — 2) l а + — N (n) — N (n — 1) +

1 (1

2 2

+ — N (и — 2)i o . 16) Это выражение описывает параболу второго порядка, проходящую через точки N (n — 2), 40 N(n — 1) и И(и), в чем легко убедиться, подставляя в формулу (6) значения о=О, о= — 1, о= — 2 и получая N(n), N(n — 1), Л((и — 2) соответственно.

Постоянная преобразователей 7, 8 и 9 Т=

45 2m должна быть вдвое меньше интервала

Fo квантования Т, что обеспечивается соответствующим выбором Ро.

Блок синхронизации 20 в зависимости от знака sign F„ переключает реверсивный счетчик 21 на сложение, либо на вычитание. Получение производной в виде частотно-импульсного сигнала позволяет ввести в преобразова55 тель простую схему изменения порядка экстраполяции при скачках входного сигнала. Так как воспроизводимая величина имеет непрерывную во времени и ограниченную по модулю производную x(t), то на положительном выходе третьего вычислительного блока 13 импульсов не будет, так как в нормальном режиме F; (Р; триггеры 18 и 19 находятся в нулевом состоянии и на запрещающий б5 вход блока синхронизации 20 подается «О».

550641

При скачках входного сигнала производная резко возрастает, первый же импульс на noJIo?KHTeJIbHoM выходе вычислительного блока

13 устанавливает триггер 18 в «I», блок 20 запирает вход реверсивного счетчика 21, третий элемент И 6 открывается и тактовые импульсы проходят на счетный вход триггера

19. Первый из них устанавливает его в «1», второй сбрасывает в «О». При этом обнуляется триггер 18 и запирающий сигнал на входе блока 20 обращается в «О». К этому времени в памяти экстр аполирующего преобразователя у?ке имеются три значения, принадлежащие одной параболе, и вновь осуществляется экстраполяция второго порядка. Таким образом, при каждом скачке входного сигнала на 2Т запирается вход реверсивного счетчика 21, что обеспечивает в течение 2Т экстраполяцию нулевого порядка путем записи N(n) в реверсивный счетчик 21.

Применение данного экстраполирующего преобразователя обеспечивает более высокую точность, отсутствие перерегулирования, формирует кроме экстраполированного значения кода экстраполированные значения первой н второй производных в виде частоты следования импульсов, что позволяет существенно упростить ряд систем автоматизированного управления и, в частности, станков с программным управлением и частотно-управляемых электроприводов.

Формула изобретения

Цифровой экстраполирующий преобразователь, содержащий первый регистр, входы которого соединены с установочными входами реверсивного счетчика и с кодовым входом преобразователя, а выходы — со входом первого преобразователя «код-частота» и через последовательно соединенные первый элемент

И, второй регистр, подключенный ко второму преобразователю «код-частота», второй элемент И и третий регистр — со входами третьего преобразователя «код-частота», причем управляющие входы первого и второго элементов И подключены к тактовому входу

5 преобразователя, отличающийся тем, что, с целью повышения точности преобразователя, в него введены четыре триггера, первый вычислительный блок, блок синхронизации и последовательно соединенные суммирующий счетчик, четвертый преобразователь «кодчастота», блок коммутации, второй вычислительный блок, входы которого подключены к выходу второго преобразователя «код-частота» и единичным выходам первого, второго и

15 третьего триггеров, а выходы через блок синхронизации — ко входам реверсивного счетчика, третий вычислительный блок, пятый триггер, третий элемент И, управляющий вход которого подключен к тактовому входу преобразователя и входу установки в нуль суммирующего счетчика, и шестой триггер, единичный выход которого подключен к нулевому входу пятого триггера, счетные входы второго и четвертого триггеров подсоединены к выходам соответственно первого и третьего преобразователей «код-частота», единичные выходы этих триггеров, подключенные к счетным входам первого и третьего триггеров соответственно, и выход второго преобразователя «код-частота» з соединены через первый вычислительный блок со входами блока коммутации и четвертого преобразователя «код-частота», причем единичный выход пятого триггера подключен к запрещающему входу блока синхронизации.

Источники информации, принятые во внимание при экспертизе

1. Коршунов IO. M. Цифровые сглаживаю4п щие и преобразующие системы, М., «Энергия», 1969 r, стр. 53 — 55.

2. Лвторское свидетельство СССР М?486321

М. Кл. G 06 F 15/20, 05.04.74 (прототип).

550641

Составитель Н. Велинкова

Редактор Н, Каменская Техред М. Семенов Корректор А. Галахова

Заказ 612/9 Изд. № 271 Тираж 899 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий! 13035, Москва, К-35, Раушская наб., д. 4/5

Тппограбия, пр. Сапунова, 2