Цифровой линейный интерполятор

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИНА ВВХВ11

ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 08.05.75 (21) 2131670/24 с присоединением заявки №(23) Приоритет—,, е

) И; КЪ.

Й

G05 В 19/18

Государственный квинтет

Совета Мнннстроо СССР но делам нзебретеннй и открытнй (43) ОпУбликовано 25.03.77Бюллетень № 11 (53) УДК 621-503. .55 (088.8) (45) Дата опубликования описания 08.07.77 (72) Авторы изобретения

А. А. Плавильшиков и В. М. Трушин (71) Заявитель (54) ЦИФРОВОЙ ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР

Изобретение относится к автоматике и вычислительной технике и, в частности, к устройствам регистрации информации.

Известен линейный интерполятор, со» держаший собирательную схему, последовательно соединенные регистр, .в который записывается код тангенса угла..наклона интерполируемого участка, вентили, сумматор, схему анализа знака и счетчик, в который записывается код большего прирашения координаты. Такие интерполяторы сложны, работа их возможна только в комплексе с вычислительной машиной, т.и. в каждом цикле преобразования необходимо сравнивать приращения, определять боль-1S шее из них и вычислять тангенс угла наклона.

Наиболее близким техническим решением к данному изобретению является -;цифровой линейный интерполятор, содержаший пос- оп ледовательно соединенные блок управления, генератбр импульсов, делитель частоты, выход кбторого подключен к первому входу первого счетчика и к первому входу второго счетчика, второй вход первого счетчика под-д ключен к выходу первого блока сравнения и к первому входу блока управления, а выход первого счетчика подключен ко входу первого блока сравнения, второй вход которого соединен со вторым входом делителя частоты и выходом первого регистра прирашений, вход которого соединен с одним из выходов блока управления, один из. выходов которого через второй регистр приращений подключен к третьему входу делителя частоты и к первому входу второго блока сравнения, второй вход которого подключен к выходу второго счетчика, а выход второго блока сравнения подключен ко вторым входам второго счетчика и блока управления. Недостатком этого интерполятора является то, что частота импульсов в унитарном коде на его выходе только в среднем пропорциональна заданному числу, Это приводит к увеличению погрешности интерполяции, т.к. отклонение фактической траектории движения регистрирующего органа от исходной прямой линии, определяемое степенью неравномерности число-импульсного кода, будет большим.

5516 хо

fg о у

4 Х где К вЂ” коэффициент пропорциональности.

Следовательно, отношение скоростей отПель изобретения — повышение точности инт рполятора.

Это достигается тем, что интерполятор содержит третий счетчик, первый вход которого соединен со вторым bxoaoMnepsuro счетчика, третий блок сравнения, первый вход которого соединен с выходом третьего счетчика, второй вход которого подключен к выходу второго регистра приращений, а выход подключен к третьему входу блока управления и ко второму входу третье го счетчика, четвертый счетчик, первый вход которого соединен со вторым входом второго счетчика, и четвертый блок сравнения, первый вход которого подключен к ® выходу четвертого счетчика, второй вход четвертого блока сравнения соединен с выходом первого регистра приращений, а выход четвертого блока срав, ненни — с четвертым входом блока управления и со вторым входом четвертого счетчика.

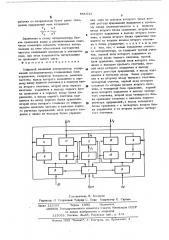

Блок-схема интерполятора представлена на чертеже.

Интерполятор содержит блок управления

1, генератор импульсов 2, делитель частоты 3, первый счетчик 4, второй счетчик 5, первый блок сравнения 6, второй блок сравнения 7,первый регистр приращения Я (,4 X ), второй регистр «риращения 9 (ь Y ), третий счетчик 10, четвертый счетчик 11, третий блок сравнения

3.2 и четвертый блок сравнения 13.

Интерполятор работает следующим об разом. 35

По сигналу "Пуск блок управления 1 разрешает запись кодов приращений координат h Х и Ь У в регистры 8 и 9 и поступление импульсов иэ генератора 2, который соединен со входом делителя часто-,р ты 3,- имеющего несколько выходов. Выбор одного из выходов делителя частоты осуществляется в зависимости от величин приращений координат так, что, чем больше приращения координат, тем меньше коэффициент ц деления делителя частоты и выше частота Д.

Импульсы с частотой 1о поступают на счетные входы счетчиков 5 и 4; Поступление импульсов в счетчики 4 и 5 продолжается до момента срабатывания соответствующих им блоков сравнения 6 и 7, которые выда ют сигиал в момент равенства числа импульсов „накопленных в соответствующем счетчике и числа в соответствующем регистре. При этом происходит установка счетчиков 4 и 5 в состояние 0 по сиг налам с блоков сравнения 6 и 7 и.новое нх заполнение; импульсами до очередного срабатывания блоков сравнения. Этот процесс происходит непрерывно. 60

11

Выходные сигналы блоков сравнения образуют унитарные коды. Частоты следования импульсов в унитарных кодах по координатам равны: причем мгновенные значения этих частот за

° время преобразования остаются постоянны ми. При этом число импульсов в унитарном коде кажцого из каналов равно числу, записанному в регистре данного канала, т.е. приращению по каждой иэ координат. Дейст вительно, импульсы с частотами следования х и „ поступают на счетные входь| х соответствующих счетчиков — 10 и 11.

Накопление импульсов и счетчиках 10 и

11 происходит до момента срабатывания блоков сравнения 13 и 12, которые выдают в блок управления 1 сигнал в момент равенства числа импульсов, накопленных в соответствующем счетчике и числа, записанного в соответствующем регистре. По сигналам с блоков сравнения 13 и 12 блок управления 1 прекращает поступление импульсов на счетчики 4 и 5.

Если приращение по какой-либо иэ координат, например h Х, будет равно О, то блок управления 1 по совпадению сиг нала Пуск и сигнала, который выдастблок сравнения 6, заблокирует выход блока сравнения 7 и на выходе интерполятора по координате Х импульсы унитарного кода будут отсутствовать. Не будут поступать импульсы и на вход счетчика 11. Кроме того, блок управления 1 запишет единицу в младший разряд регистра 8. Таким образом, импульсы унитарного кода с выхода блока сравнения 6 будут поступать на яыход интерполятора по каналу Y " и на счетный вход счетчика 10 с максималь-. ной частотой, равной f . Процесс преобразования заканчивается при срабатывании блока сравнения 12, который выдает сигнал в блок управления 1 при равенстве числа импульсов, накопленных в счетчике

10 и числа, записанного в регистре 9.

Таким образом, на выходах интерполятора получаются унитарные коды, частоты следования импульсов в которых, а значит и скорости отработки исполнительных систем по каждой иэ координат, обратно пропорциональны величине приращения по другой координате. о 4 „-К =K» V -Êf =К

551611

С оставитель B. Комаров

Редактор Л. Сторчевая Техред С. Беца Коррекгор Е. Скучка

Заказ 123/25 Тираж . 1095 Подписное

ЫНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., a. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 работки по координатам будет равно отно.шению приращений этих координат: дХ ьУ

Включение в схему интерполятора блоков сравнения кодов и дополнительных счетчиков позволило повысить точность интерполяции за счет обеспечения постоянства частоты следования импульсов в унитарном. коде, при этом погрешность интерполяции не превышает одного шага.

Формула изобретения цифровой линейный интерполятор, содержащий последовательно соединенные блок управления, генератор импульсов, делитель частоты, выход которого подключен к первому входу первого счетчика и к первому входу второго счетчика, второй вход первого © вчетчика подключен к выходу первого блока сравнения и к первому входу блока управления, а выход первого счетчика подключен ко входу первого блока сравнения, второй вход которого соединен со вторым входом делителя частоты и выходом первого регистра приращений, вход которого соединен с одним из выходов блока управления, один из выходов которого через второй регистр приращений подключен к третьему входу делителя частоты и к первому входу второго блока сравнения, второй вход которого подключен к выходу второго счетчика, а выход второго блока сравнения подключен ко вторым входам второго счетчика и. блока управления, о т л и ч а ю щ ийс я тем, что, с целью повышения точности интерполятора, он содержит третий счегчик, первый вход которого подключен ко второму входу первого счетчика, третий блок сравнения, первый вход которого соединен с выходом третьего счетчика, второй вход которого подключен к выходу второго регистра приращений, а выход под ключен к третьему входу блока управления и ко второму входу третьего счетчика, четвертый счетчик, первый вход которого соединен со вторым входом второго счетчика, и четвертый блок сравнения, первый вход которого подключен к выходу четвертого счетчика, второй вход четвертого блс ка сравнения соединен с выходом первого регистра приращений, а выход четвертого блока сравнении — с четвертым входом блока управления и со вторым входом четвертого счетчика.