Устройство для ввода информации

Иллюстрации

Показать всеРеферат

ОП ИОАН-И-Е

ИЗОБРЕТЕНИЯ

Союз Советских

Совреалистииеских

Рвсяубпик (11) 551 633

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свил-eyИ 492871. (51) М. Кл. г

Ст06 Р 3/00 (22) Заявлено 08.08.75 (21) 2161458/24 с присоединением заявки № «« (23) Приоритет(43) Опубликовано 25,03.77.Бюллетень №11 (45) Дата опубликования описания 06.09.77

Гасударственный номнтет

Совета Мнннотроа СССР по делам изобретений и открытей (53) УДК 681 14 (088.8) (72) Авторы изобретения

В. А. Солодовников, В. П. Дудалев, Г. М. Солодихин и В Н. Васильев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ

Изобретение относится к области вычислительной техники и может быть использо вано в .автоматизированных системах обра ботки экспериментальной информации. .По авт. св. М 492871 известно ycw 5 ройство для ввода информации, используемое в различных автоматизированных системах обработки экспериментальной информации.

Н ед остат ком устройства является то, что- оно не может функционировать B ком- т0 плексах автоматизированной обработки экспериментальных данных на базе ЭВМ, осуществляюших обмен с внешними устр ойсч вами только побайтно.

Цель изобретения - расширить функцис - 15 нальные возможности устройства.

Это достигается тем, что в устройство введены счетчик байтов, дешифратор байтов, буферный регистр, группа алементов И, элементы ИЛИ, элементы НЕ, и элемент за- 0 держки, причем вход буферного регистра соединен с выходом сдвигового регистра, выход инвертора сброса соединен с первыми входами счетчика байтов и первого элемента ИЛИ, выход которого подключен к 2б первому выходу устройства, вторые входы счетчика байтов и первого элемента ИЛИ соединены с выходом первого алемента НЕ, первый вход которого соединен с выходом второго элемента НЕ, выход элемента задержки .соединен со вторым входом перво-, го элемента НЕ, выход счетчика байтов сое динен с входом дешифратора байтов, выхо ды .которого соединены соответственно с первым входом каждого из группы алемен .. тов И, вторые входы которых соединены соответственно с выходами разрядов буферно- го регистра, третьивходыэтих -алементов И объединены и соединены с входом устройся ва и входом элемента задержки, выходы всех элементов И группы соединены соот ветственно с входами второго элемента ИЛИ, выход которого соединен со вторым выходом устройства, вход второго алемента НЕ соединен с последним выходом дешифратора байтов.

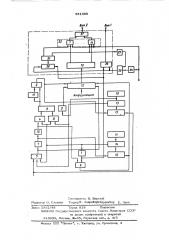

На чертеже представлена структурная электрическая схема устройства.

Устройство содержит инвертор сброса 1, вентиль управления 2, дешифратор разрядов

551 633 з

3, вэнтнль установки 4 тиль 5 разрешения записи, вентиль сброса 6, дифференцирующую

aem 7, элемент ИЛИ 8, триггер 9, регистр

10 числа разрядов, регистр 11 числа слов, сдвиговый регистр 12, блок 13 сравнения разрядов, блок 14 сравнения слов, счетчик

l5 числа разрядов, счетчик 16 числа слов, генератор импульсов 17, элемент задержки 18, буферный регистр 19, счетчик байтов 20, дешифратор байтов 21, группу элементов И (вентилей байтов) 22, эле» мент НЕ (инвертор запрета) 23, элемент задержки 24, элемент НЕ (вентиль готовности) 25, элемент ИЛИ (сборка сигналов готовности) 26, элемент ИЛИ (сборка байтов) 27.

Устройство работает следующим образом.

В регистр 10 заносится число разрядов входного информационного слова. Состояние регистра дешифрируется дешифратором 3,, 20 который своим выходом управляет прохождением соответствующего количества разрядов информации на сдвиговый регистр 12.

На регистре 11 задается требуемое число входных слов, необходимых для формированпя25 машинного слове. Слова входной информации поступают в младшие разряды блока 12, а импульсы сопровождения информационных слов (заявки) поступают на вход вентиля 5 и вход сброса счетчика 15, Два других 30 входа вентиля 5 управляются выходами блоков 13 и 14. Заявка, пройдя вентиль 5, разрешает запись информации в выходной сдвиговый рсгистр 12. На элементе 7 выделяется задний фронт заявки, который пос» 35 тупает на счетный вход счетчика 16, подсчитывающего количество входных ипфорл1ационпых слов, задерживается па элементе задержки 19 и через вентиль установки 4, который управляется выходом блоха 14, 0 перебрасывает в еднппчпое состояпие трпггер

9. Тем самым запускается генератор 17, импульсы с которого через вептиль 2 произ» водят сдвиг содержимого регистра 12 в сто. рону старших разрядов. Одновременпо эти )45 же импульсы поступают па счетный вход счетчика 15, подсчитывающего количество сдвиговых им пульс ов, Ка к т олько информацияцня в сдвиговом регистре 12 сдвипется, освободив младшпо разряды, на количество 50 разрядов, заданное в регистре 10, потенциал на выходе блока 13 сбросит через элемент ИЛИ 8 триггер 9 в нулевое состояние, запретит прохождение импульсов сдвига па вход блока 12 через вентиль управления 2. Частота -еператора 17 подобрана таким образом, чтобы заданное количество сдвигов успевало пройти до прихода следую..щей заявки, Кпкл занесения входных информационных слов в младшие разряды регпстра 12 и сдвиг информации в сторону стар.. щих разрядов повторяется до тех пор, пока содержимое счетчика 16 не совпадет с кодом, заданным на регистре.11 числа слов

Потенцйал на выходе блока 1 4 сравнения слов запрещает прохождение задержанной заявки через вентиль установки 4, grpgrrep

9 остается в нулевом состоянии, и сдвиг . s сдвиговом регистре 12 не происходит, Одновременно разрешающий потенциал с инsepropa сброса 1 сбрасывает счетчик 20, записывает парафа эным кодом сформирован ное машинное слово в буферный регистр 19 и выдает через элемент 26 сигнал Готовность в ЗВМ; Задержанная заявка проходит через вентиль 6, открытый потенциалом инвертора 1 при сбросе счетчика 16 и регистра 12, тем самым подготавливая уст ройство для формирования следующего машинного слова.

На сигнал Готовность" ЗВМ выдает сит нал приема информации, по которому через первый К-разрядный вентиль байтов-22, открытый разрешающим потенциалом с дешифратора 21, и сборку байтов 27 в ЗВМ, для записи выдается младший байт сформиро»ванного машинного слова. Задержанный на элементе задержки 24 сигнал приема ин формации добавляет +1" в счетчик 20 и через сборку 26 поступает в ЗВМ как следующий сигнал Готовность . Потенциал с дешифратора байтов 21 разрешает прохождение информации в ЗВМ через второй вентиль байтов 22 и т. д. (общее количество вентилей байтов 22 в устройстве зависит от формата полноразрядного машинного слова

ЗВМ и равно целому числу П, где Я =тП Ц;

К - число разрядов байта, Тп - разрядность машинного слова ЭВМ). После выдачи в

ЗВМ последнего информационного байта потепциал с пнвертора 23 запрещает прохождение задержанного сигнале приема информации через вентиль готовности 25 и запись информации в ЭВМ прекрашается до прихода следуюшего разрешающего потенциала с ин вертора 1..

Устройство может работать в комплексе с ЭВМ, имеюшими режим обмена с внешними устройствами полноразрядными машинными словами. При этом информацию в ЗВМ необходимо выдавать с выхода сдвигового регистра 12.

Предлагаемое устройство для ввода информации предназначено для функционировании в составе специализпровапной аппаратуры электрического и логического сопряжения различных источников экспериментальной информации с ЗВМ и является ее выходным узлом. Устройство подключается к каналам (мультнплексному или селекторному) ввода551633 вывода ЭВМ как внешнее устройство ЭВМ, производит рациональную плотную упаковку" ,машинных слов из входных слов различной разрядности и последующий побайтный обмен с ЭВМ, что позволяет осуществить em». 5 тивную загрузку памяти ЭВМ при обработке экспериментальной информации.

Формула изобретения

1Î

Устройство для ввода информации по авт. св. Ни 492871, о т л и ч а ю щ ее с я тем, что, с целью расширения функциональных возможностей, в него введены счетчик байтов, дешифратор байтов, буфер !5 ный регистр, группа элементов И, элементы ИЛИ, элементы НЕ и элемент задержки причем вход буферного регистра соединен с выходом сдвигового регистра, выход инвертора сброса соединен с первыми входа- Я ми счетчика байтов и первого элемента ИЛИ, выход которого подключен к первому вье ходу устройства, вторые входы счетчика байтов и первого элемента ИЛИ соединены с выходами первого элемента НЕ, первый вход которого соединен с выходом второго элемента НЕ, выход элемента задержки соединен со вторым входом первого элемэвс та НЕ, выход счетчика байтов соединен с входом дешифр тора байтов, выходы которв» го соединены соответственно с первым, вхо дом каждого из группы элементов И, вторые входы которых соединены соответственно с выходами разрядов буферного регистра третьи входы этих элементов И объединены и соединены с входом устройства и входом элемента задержки, выходы всех элементов

И группы соединены соответственно с вхо дами второго элемента ИЛИ, выход которо го соединен со вторым, выходом устройства, вход второго элемента НЕ соединен с поо

: ледним выходом дешифратора байтов.

55 1033 вихр

Составитель В. Вертлиб

Техред Н. Лндрейчук Корректор Е. Папп

Редактор О. Степина

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Заказ 2861/48 Тираж 818 Подписное

ПНИИПИ "îñóäàðñòâåííîãî комитсга Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж»35, Раушская наб., д. 4/5