Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

г :.ока.т Г оветскик

С.оциаимстнчесяик

Рестгубпии

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (») 551702 (61) Дополнительное к авт, свид-ву— (22) Заявлено 03,11.75 (21) 2186052/24 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано 25.03.77. Бюллетень № 11 (4б) Дата опубликования описаяия15.06.77 (51) М Кл о 611C19/00

Государстввнный комитет

Совета Министров СССР по двлам иэоорвтвний и открытий (53) УДК 681.327.6 (088.8) (72) Авторы изобретения

А, И,Журавлев и В, Г. Чибисов (71) Заявитель

Особое конструкторское бюро вычислительной техники Рязанского радиотехнического института (54) БУФЕРНОЕ ЗАПОМИ11А101ЦЕЕ УСТРОЙГГВО

Известное буферное запоминающее устройство содержит поразрядно соединенные регистры, ячей* ки управления считыванием и записью, логические элементы И.

НеДостатками известного устройства являются иевьтсокат1 скорость работы и большие аппаратур. ные затраты.

Наиболее близко к изобретению буферное запоминающее устройство, которое содержит и ре* гистров, одноименные разрядные шины которых соединены последовательно, входы записи регист. ров, кроме первого, подключены к выходам элементов И, п триггеров, выходные элементы И,входы которых соединены с разрядными выходами и-го регистра и n— - го элемента И, и шину тактовых импульсов.

Однако это устройство обладает низким быстродействием, поскольку управление выполнено по многотактной схеме, а регистры выполнены на триггерах с пассивной записью.

Цель изобретения — повышение быстродействия устройства, Это достигается тем, что буферное запоминающее устройство содержит п элементов ИЛИ первой групбы, и — 1 элементов HJ IH второй группы, эле2 менты НЕ ио числу четных регистров, единичные выходы триггеров подключены к первым входам одноименных элементов ИЛИ первой группы, нулевые выходы триггеров, кроме первого,— к первым входам одноименных элементов ИЛИ второй груп. пы, выходы элементов ИЛИ первой группы соединены с первыми входами одноимешипх элементов

И, выходы элементов ИЛИ второй группы соединены со вторыми входами предыдущих элементов

10 И, выходы элементов И подключены ко вторым входам одноименных элементов ИЛИ первой группы и, кроме п-го элемента И, — ко вторым входам последующих элементов ИЛИ второй группы, третьи вХоды нечетных элемептов И соединены с шиной тактои вых импульсов, подключенной через элементы HF к третьим входам четных элементов И.

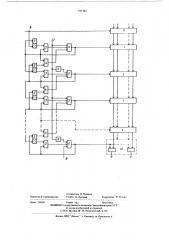

На чертеже дана схема предлагаемого устройства.

Устройство содержит и регистров 1, одноименные разряды которых соединены последовательно, п триггеров 2, элементов ИЛИ 3 первой группы, п-1 элементов ИЛИ 4 второй группы, и элемен26 I тов И 5, элементы III. 6 по числу четных регистров

551 702

l, шину 7 тактовых импульсов, шину 8 записи информации.

Единичные выходы триггеров 2 подключены к первым входам одноименных элементов ИЛИ 3 первой группы, нулевые выходы триггеров 2, кро ме первого (верхний на чертеже), — к первым входам одноименных элементов ИЛИ 4 второй группы, выходы элементов ИЛИ 3 первой группы соединены с первыми входами одноименных элементов, И 5, выходы элементов ИЛИ 4 второй группы соединены со вторыми входами предыдущих элементов И 5.

Выходы элементов И 5 подключены ко вторым входам одноименных элементов ИЛИ 3 первой группы и, кроме и-го элемента И (нижний на чертеже), — ко вторым входам последующих элементов ИЛИ 4 торой группы, третьи входы нечетных элементов И 5 соединены с шиной 7, подключенной через элементы НЕ 6 к третьим входам четных элементов И 5. Ко входу первого триггера 2 подключена шина 8, ко входу последнего элемента

И 5 — шина 9 считывания информаций. Устройство также содержит выходные, элементы И 10 для вывода информации и входной регистр 11.

Устройство работает следующим образом.

На шину 7 постоянно r.эступают тактовые импульсы, частота которых не ниже частоты записи информации. Для записи информации в запоминающее устройство на шину 8 поступает импульс, по которому первое слово записывается в регистр 11, одновременно первый триггер 2 устанавливается в единичное состояние. Единичный потенциал с выхода первого триггера 2, проходя через первый элемент ИЛИ 3, открывает по первому входу первый элемент И 5. По второму входу элемент И 5 в этот момент открыт потенциалом с элемента ИЛИ 4.

Тактовый. импульс, проходя первый элемент И 5, устанавливает первый триггер 2 в нулевое состояние, а второй триггер 2 — в единичное и переписывает ин.формацию из регистра 11 в первый регистр 1.

По заднему фронту тактового импульса срабатывает второй элемент И 5, второй триггер 2 устанавливается, в нулевое состояние, третий триггер 2 — s единичное, и слово из первого регистра 1 переписывается во второй регистр 1.

Дальнейшее продвижение информации из регистра в регистр осуществляется аналогично.

Обратная связь между элементами И 5 и.элементами ИЛИ 3 и 4 предотвращает "обрезание" импульсов на выходе элементов И 5, обеспечивая

Буферное запоминающее устройство, содержаИ щее п регистров, одноименные разрядные шины которых соединены последовательно, а входы записи регистров, кроме первого, подключены к выходам элементов И, и триггеров, выходные элементы

И, входы которых соединены с разрядными выхоЭО дами n — го регистра и n — го элемента И, и шину тактовых импульсов, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия, оно содержит пэлементов ИЛИ первой группы,,n — элементов

ИЛИ второй группы, элементы НЕ по числу четных регистров, единичные выходы триггеров подключены к первым входам одноименных элементов ИЛИ первой группы, нулевые выходы триггеров, кроме первого, — к первым входам одноименных элементов ИЛИ второй группы, выходы элементов ИЛИ

4О первой группы сое1шнены с первыми входами одноименных элементов И, выходы элементов ИЛИ второй группь| соединены со вторыми входами предыдущих элементов И, выходы элементов И подключены ко вторым входам одноименных эле © ментов ИЛИ первой группы и, кроме и — го элемента

И, — ко вторым входам последующих элементов

ИЛИ второй группы, третьи входы нечетных элементов И соединены с шиной тактовых импульсов, подключенной через элементы НЕ к третьим входам бО четных элементов И. б !

О

1б

20 надежную перезапись информации из регистра в регистр и установку триггеров 2, Через - тактовых импульсов (где n — количество регистров 1) первое слово окажется в последнем, и — ом регистре.

При считывании информации на шину 9 считывания информации подается импульс и первое слово через эле.ленты И 10 выводится из устройства. Если последующий регистр 1 занят, то сигнал с нулевого выхода триггера 2 поступает через одноименный элемент ИЛИ 4 на вход элемента И 5 предыдущего разряда, блокируя перезапись информации в этот регистр. При освобождении последующего регистра происходит обнуление соответствующего триггера и разблокировка элемента И 5, служащего для перезаписи информации из предыдущего регистра.

По переднему фронту тактового импульса переписывается информация из четного регистра 1 в нечетный, по заднему фронту происходит перезапись информации из,нечетного регистра 1 в четный.

Формула изобретения

Составитель В. Рудаков

Техред О. Лутовая

Корректор И. Гоксяч

Редактор Л. Гребенникова

Заказ 130/28

Филиал ППП " Патент ", г. Ужтород. ул. Проектная, 4

Тираж .762 Полллсное

ЦНИИПИ Государственного комитета Совета Министров СССР но делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская иаб., д. 4/5