Устройство для синхронизации операндов в однородных структурах

Иллюстрации

Показать всеРеферат

00 552600

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВЙДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 11.07.73 (21) 1944665, 24 с присоединением заявки № (23) Приоритет

Опубликовано 30.03.77. Бюллетень № 12

Дата опубликования описания 11.04.77 (51) М. КлР G 06F 1/00

Государственный комитет

Совета Министров СССР (53) УДК 681.325.5 (088.8) ао делам изобретений и открытий (72) Авторы изобретения

Г. Г. Асатиани, В. В. Игнатущенко, Л. И. Панцхава и В. Г. Чачанидзе

Ордена Ленина институт проблем управления (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ОПЕРАНДОВ

В ОДНОРОДНЫХ СТРУКТУРАХ

Изобретение относится к области автоматики и вычислительной техники и может найти применение для построения цифровых устройств на базе однородных микроэлектронных структур (ОС).

Известно устройство синхронизации операндов в ОС, содержащее две схемы выделения маркерных сигналов операндов, на вход одной из которых подается операнд а, а на вход другой — операнд в. Каждая из этих схем состоит из триггеров с раздельными входами, схем

НЕ, И и задержки на один такт. Выход одной схемы выделения маркерных сигналов соединен с входом другой аналогичной схемы и с входом статического регистра записи и хранения первого по времени операнда а. Каждый разряд регистра состоит из триггера с раздельными входами, схемы И и четырех схем задержки на один такт. Другой вход регистра соединен с шиной операнда а, а выходы — с входами схемы считывания и выдачи этого операнда, причем каждый разряд этой схемы имеет схему И и три схемы задержки на один такт; другой вход схемы связан с выходом схем выделения маркерных сигналов операнда в. Выход схемы выделения маркерных сигналов операнда в подключен также к входу аналогичной схемы операнда а. Операнд в подается на вход линии задержки, каждый разряд которой содержит одну схему задержки на один такт.

Такое устройство имеет ряд недостатков, основные из них — сложность и жесткое раз5 деление устройства на два канала: канал для передачи опережающего операнда и канал для передачи оставшегося операнда, что осложняет коммутацию операндов на вход устройства и делает невозможным применение устройства

10 для синхронизации операндов, когда неизвестен порядок их следования. Кроме того, в устройстве не предусмотрен его запуск при помощи специального управляющего сигнала как самостоятельного оператора вычислитель15 ной машины.

Цель изобретения — упрощение коммутации операндов на вход устройства и расширение области его применения.

Это достигается тем, что в устройстве выхо20 ды регистров хранения операндов соединены с соответствующими информационными выходами устройства через схемы И, другие входы которых связаны с единичным выходом триггера управления, выходы регистров хранения

25 операндов — с единичными входами соответствующих триггеров управления регистрами через соответствующие схемы И, другие входы которых через соответствующие схемы НЕ подключены к единичному выходу триггера

552600

55 бО б5 управления, Нулевые входы триггеров управления регистрами соединены с единичным выходом триггера управления, а единичные выходы через первую и вторую схемы задержки — соответственно с управляющими входами регистров хранения операндов и с первым и вторым входами схемы И, третий вход которой подключен к единичному выходу триггера хранения сигнала запуска, а выход — к единичному входу триггера управления, единичный выход которого через третью схему задержки соединен с нулевыми входами триггера управления и триггера хранения сигнала запуска.

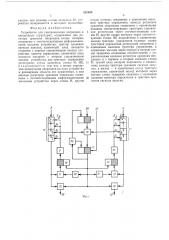

Функциональная схема устройства для синхронизации операпдо» » ОС цредст.inлена на фиг. 1, а на фиг. 2 — тii жс схема, вложенная ь ОС.

Функциональная схема устройства (фиг. 1) содержит регистры 1, 2 хранения операндов, работающие в зависимости от значения управляющих сигналов как в режиме статического регистра, так и в режиме сдвигающего регистра; информационные входы 3, 4 устройства для приема операндов; управляющие входы

5ь 5, 5З, ..., 5 /4 регистра 1, при этом общее количество этих входов в четыре раза меньше числа тактов, так как ячейка ОС реализует четыре разряда регистра; управляющие входы

6i, 6, бз, ..., 6"/4 регистра 2; информационные связи 7i, 7а, 7з, ..., 7 /< i между разрядами регистра 1; информационные связи 8i, 8,..., 8 /, < между разрядами регистра 2; схемы задержки 9, 10; схемы И 11 15; триггер 16 хранения сигнала запуска; триггер 17 управления; триггеры 18, 19 управления регистрами 1, 2; схемы НЕ 20, 21; схему задержки 22; управляющий вход 23 для установки устройства в исходное положение; управляющий вход 24 устройства для приема сигнала его запуска, т. е. сигнала разрешения одновременной выда чи устройством операндов; информационные выходы 25, 26 устройства.

Устройство для n=32 реализовано в ОС следующим образом (см. фиг. 2), регистры 1, 2 выполнены соответственно на ячейках 27i—

27 и 28i — 28, при этом каждая ячейка реализует по четыре разряда регистра. Устройство имеет информационные входы 29, 30, управляющие входы 31 ячеек 27 регистра, управляющие входы 32 ячеек 28 регистра, информационные связи 33 между разрядами ячеек 27, информационные связи 34 между разрядами ячеек 28. Цепь единичный выход триггера 18 (19) — задержка на один такт 9(10) реализована в ОС при помощи цепи нулевой выход триггера — задержка на один такт с инвертированием 35 (36); схемы И 11 — 15 — при помощи ячеек 37 — 41, а триггеры 16 — 19 — соответственно парами ячеек 42, 43, 44 и 45, настроенных на реализацию функции И вЂ” НЕ.

Цепь единичный выход триггера 17 — нулевой вход триггера 18 реализована при помощи цепи нулевой выход ячейки 43 — схема НЕ

46 — нулевой вход ячейки 44; цепь единичный выход триггера 17 — схема НЕ 20 (21)— схема И 11 (13) — цепью нулевой выход ячейки 43 — схема НЕ 46i — схема НЕ 46 — ячейка 37(39); цепь единичный выход триггера

17 — схема И 12(14) — цепью нулевой выход ячсйки 43 — схема НЕ 46i — схема НЕ 46 — схема НЕ 47 — ячейка 38(40). Схема задержки на 32 такта выполнена на ячейках 48i — 48 .

Устройство имеет вход 49 для установки его в исходное положение, вход 50 для приема сигнала запуска, информационные выходы 51, 52.

Таким образом, устройство реализовано в ОС при помощи 50 ячеек с размерами окаймляющего прямоугольника 7)(8.

Работает устройство следующим образом.

Па вход 23 устройства, подается сигнал, который устанавливает триггер 17 в единичное состояние. Далее триггер 17 устанавливает в нулевое состояние триггеры 18, 19, через схемы задержки 22 себя и триггер 16. Регистры 1 и 2 переводятся в нулевое положение при настройке ОС. После этого устройство готово для приема операндов и сигнала запуска. Исходное положение устройство занимает один раз при включении цепей питания ОС. Порядок поступления на устройство операндов и сигнала запуска не имеет значения. Устройство начинает выдачу операндов при наличии обоих операндов и названного сигнала. Каждый операнд снабжен единицей головки (маркерным сигналом). Пусть на устройство вначале поступил операнд на вход 3. Так как триггер 18 находится в нулевом состоянии, то через схемы задержки 9 на управляющие входы регистра 1 проходят нули и регистр 1 работает как сдвигающий регистр. Через определенное число тактов (для фиг. 2 через 32 такта) на выходе регистра 1 появляется единица головки операнда, который перебрасывает триггер 18 через схему И 11 в единичное положение, так как на выходе схемы НЕ 20 име ется также единица. Единица с выхода триггера 18 через схемы задержки 9 поступает на управляющие входы регистра 1. Так как эта единица задерживается на такт, регистр 1 успевает сделать сдвиг на разряд и гасится единица головки, после чего регистр 1 переходит в режим статического регистра. Аналогичным образом попадает в регистр 2 второй операнд.

Сигнал запуска через вход 24 устанавливает триггер 16 в единичное состояние. На выходе схемы И 15, при наличии обоих операндов, в этот момент появляется единица, которая перебрасывает триггер 17 в единичное положение. Единица на выходе триггера 17 при помощи схем НЕ 20 и 21 закрывает схемы И 11 и 13, открывает схемы И 12 и 14 и устанавливает триггеры 18 и 19 в нулевое состояние. На единичных выходах триггеров 18 и 19 образуются нули, которые через схемы задержки 9 и 10 поступают на входы управления регистров 1 и 2. Оба регистра переходят в режим сдвигающего регистра, и операнды через схемы И 12 и 14 поступают на информационные выходы 25 и 26 устройства. После выдачи one552600

j)dHjl0B, IlpH помощH C.. ".eMbl 3 piKI

Формула изобретения

Устройство для синхронизации операндов в однородных структурах, содержащее два регистра хранения операндов, входы которых соединены с соответствующими информационными входами устройства, триггер хранения сигнала запуска, единичный вход которого соединен с первым управляющим входом устройства, триггер управления, единичный вход которого соединен с вторым управляющим входом устройства, два триггера управления регистрами, схемы задержки, схемы И, НЕ, отл ич а ю щее с я тем, что, с целью упрощения коммутации операндов на вход устройства и расширения области его применения, в нем выходы регистров хранения операндов соединены с соответствующими информационными выходами устройства через схемы И, другие входы которых соединены с единичным выходом триггера управления, выходы регистров хранения операндов соединены с единичными входами соответствующих триггеров управле5 ния регистрами через соответствующие схемы И, другие входы которых через соответствующие схемы НЕ подключены к единичному выходу триггера управления, нулевые входы триггеров управления регистрами соединены с

10 единичным выходом триггера управления, а единичные выходы через первую и вторую схемы задержки соединены соответственно с управляющими входами регистров хранения опе рандов и с первым и вторым входами схемы

15 И, третий вход которой подключен к единичному выходу триггера хранения сигнала запуска, а выход — к единичному входу триггера управления, единичный выход которого через третью схему задержки соединен с нулевыми

20 входами триггера управления и триггера хранения сигнала запуска.

552600

ыг, Составитель А, Жеренов

Текред А. Камышникова

Корректор И. Хмелева

Редактор И. Грузова

Типография, пр. Сапунова, 2

Заказ 676/4 Изд. № 318 Тираж 899 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, K-35, Раушская наб., д. 4/5