Устройство для решения дифференциальных уравнений

Иллюстрации

Показать всеРеферат

юиеиоюзння уЖтвитно- схни . -::-.к. кж библиотека ко,:: —:,::

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (и) 552612

Софе Ооветоки»

Социалиетическик

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 24.12.75 (21) 2303224/24 с присоединением заявки №вЂ” (23) Приоритет

Опубликовано 30.03.77. Бюллетень № 12

Дата опубликования описания 11.04.77 (51) М. Кл 2 G 06F 15/32

G 06J 1/02

Государственный квмитет

Совета Министров СССР (53) УДК 681.3(088.8) ло делам изобретений и вткрытий (72) Авторы изобретения

Б. Н. Малиновский, В. П. Боюн и Л. Г. Козлов

Ордена Ленина институт кибернетики AH Украинской ССР (71) Заявитель (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЪНЫХ

УРАВНЕНИЙ

Изобретение относится к области вычислительной техники и может быть использовано при построении цифровых интегрирующих машин и однородных структур.

Известно устройство для решения дифференциальных уравнений высоких порядков (11, содержащее интеграторы, соединенные последовательно, блоки умножения, входы которых подключены к выходам соответствующих интеграторов, а выходы — к входам первого интегратора.

Недостатком этого устройства является большой объем аппаратурных затрат для решения дифференциальных уравнений высоких порядков.

Известно также наиболее близкое к изобретению устройство для решения дифференциальных уравнений, содержащее интеграторы, соединенные последовательно, блоки умножения и сумматор (2).

Известное устройство также имеет большой объем аппаратурных затрат.

Цель изобретения — упрощение устройства.

Это достигается тем, что в устройство введены регистр и узел выделения приращения.

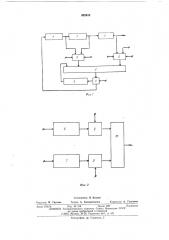

Выход сумматора соединен с первым входом узла выделения приращения, первый выход этого узла через регистр — первым входом сумматора, остальные входы которого связаны с выходами блоков умножения. Первый и второй входы каждого блока умножения I103,ключены к выходам соответствующего последующего интеграторов, а третин и четвертый входы являются входами соответствующих групп входов устройства. Второй вход узла выделения прир ащения соединен с входом устройства, а второй выход — с входом первого интегратора, выход последнего интегратора — с выходом устройства. Блок умножения содержит два регистра, два узла преобразования кодов и сумматор, выход которого соединен с выходом блока, а входы сумматора через узлы преобразования кодов — с выходами регистров, входы которых связаны с первым и вторым входами блока, входы узлов преобразования кодов — с третьим и четвертым входами блока.

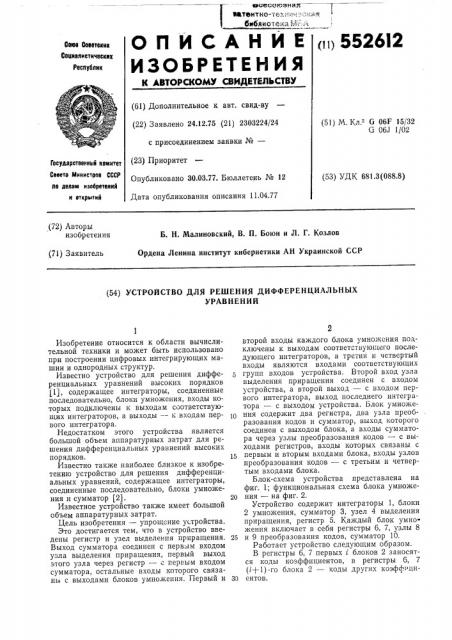

Блок-схема устройства представлена на фиг. 1; функциональная схема блока умноже20 ния — на фиг. 2.

Устройство содержит интеграторы 1, блоки

2 умножения, сумматор 3, узел 4 выделения приращения, регистр 5. Каждый блок умножения включает в себя регистры 6, 7, узлы 8

25 и 9 преобразования кодов, сумматор 10.

Работает устройство следующим образом.

В регистры 6, 7 первых i блоков 2 заносятся коды коэффициентов, в регистры 6, 7 (i+1)-ro блока 2 — коды других коэффr ци30 ентов.

552612

На (i+1)-й блок 2 подается приращение функции, а на другие блоки 2 поступают приращения переменной и ее производных.

В первом такте осуществляется выдача младшего разряда коэффициентов с регистров б, 7 на сумматоры 10, в которых вычисляются произведения приращений переменной и функции на соответствующие коэффициенты, на первый вход сумматора 3, на который в этом же такте выдается младший разряд ос"атка предыдущей итерации из регистра 5, в освободившийся разряд которого заносится с выхода сумматора 3 через блок 4 младший разряд значения правой части уравнения.

В результате работы устройства на последующих тактах вычисляются остальные разряды правой части уравнения и запоминаются в регистре 5. Затем на блок 4 подается управляющий сигнал, по которому на выход блока

4 выдаются разряды переполнения, которые поступают на первый интегратор 1. В интеграторах 1, соединенных последовательно друг с другом, осуществляется операция интегрирования и вырабатываются новые значения переполнения.

Последующие итерации осуществляются аналогично изложенному, причем значение правой части уравнения, вычисленное на предыдущей итерации и зафиксированное в регистре 5, используется в последующей итерации, поступая последовательным кодом младшими разрядами вперед на сумматор 3.

Устройство имеет меньшее количество оборудования по сравнению с прототипом, так как из устройства исключены часть блоков 2 умножения, количество входов сумматора 3 уменьшено в два раза, а дополнительно введенные узел 4 выделения приращения и регистр 5 требуют меньших затрат аппаратурных средств, чем один блок 2 умножения.

Формула изобретения

Устройство для решения дифференциальных уравнений, содержащее интеграторы, соединенные последовательно, блоки умножения и сумматор, отличающееся тем, что, с целью упрощения устройства, оно содержит регистр и узел выделения приращения, при5 чем выход сумматора соединен с первым входом узла выделения приращения, первый выход которого через регистр соединен с первым входом сумматора, остальные входы которого соединены с выходами блоков умножения, 10 первый и второй входы каждого из которых соединены с выходами соответствующего и последующего интеграторов, третий и четвертый входы каждого блока умножения являются входами соответствующих групп входов

15 устройства, второй вход узла выделения приращения соединен с входом устройства, а второй выход — с входом первого интегратора, выход последнего интегратора соединен с выходом устройства.

20 2. Устройство по п. 1, отличающееся тем, что блок умножения содержит два регистра, два узла преобразования кодов и сумматор, выход которого соединен с выходом блока, а входы сумматора через узлы преоб25 разования кодов соединены с выходами регистров, входы которых соединены с первым и вторым входами блока, входы узлов преобразования кодов соединены с третьим и четвертыми входами блока.

Источники информации, принятые во внимание при экспертизе

1. Баранов В. Л. и др. О расширении алгоритмической возможности ЦДА последоваЗ5 тельного действия, Цифровые модели и интегрирующие структуры. Труды межвузовской научной конференции по теории и принципам построения цифровых моделей и цифровых интегрирующих машин. Таганрог, 1970.

40 2. Воронов А. А. и др. Цифровые аналоги для систем автоматического управления, М., изд. АН УССР, 1960.

552612

РИе. 1

Фиг. 2

Составитель Л. Козлов

Редактор И. Грузова Техред А. Камышникова Корректор А. Галахова

Заказ 676/16 Изд. Ке 318 Тираж 899 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 5К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2