Цифровой умножитель частоты

Иллюстрации

Показать всеРеферат

(li) 552688

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сова Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 17.02.76 (21) 2325471/21 с присоединением заявки № (23) Приоритет

Опубликовано 30.03.77. Бюллетень № 12 (51) М. Кч е Н ОЗК 5/156

Государственный комитет

Совета Министров СССР (53) УДК 621.374.4 (088.8) по делам изобретении и открытий

Дата опубликования описания 26.04.77 (72) Авто р ы изобретения П. Д. Боцман, А, Н, Зеленин, А, B. Ильченко и В. П. Шинкаренко (71) Заявитель

Харьковский институт радиоэлектроники (54) ЦИФPOBOЙ УМНОЖИТЕЛЬ ЧАСТОТЫ

Изобретение относится к импульсной технике, в частности к цифровым умно>кителям частоты с переменным коэффициентом умножения, и может оыть й(спользовано В синтезаторах частоты.

Известен цифровой умно>китель частоты импульсной последовательности, содержащий два цифровых дифференцирующих устройства, которые генерируют импульсы: одно на переднем, второе на заднем фронтах входного импульса, удваивая частоты входных импульсов. Малый диапазон изменения коэффициента умно кения такого умно>кителя ограничивает возможность его применения в цифровых устройствах.

Наиболее близким к предлагаемому по технической сущности является умножитель частоты, содержа ций делитель частоты с переменным коэффициентом деления, элементы

И и последовательно соединенные дифференцирующую цепь, элемент ИЛИ и линию задержки. Наличие коммутирующих цепей с выходов каждого разряда делителя частоты усложняет этот умножитель.

Цель изобретения — упрощение умно>кителя.

Это достигается тем, что в предлагаемом цифровом умно>кителе частоты выход дифференцирующей цепи подключен к первому входу делителя частоты с переменным коэффициентом деления, выход которого через элемент И соединен с вторым входом элемента ИЛИ, а вторые входы элемента И и делителя частоты с переменным коэффициентом делен ия объединены и подключены к выходу линии задержки.

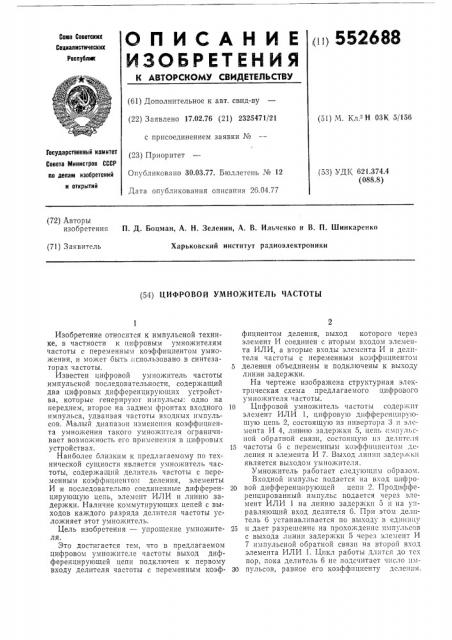

На черте>ке изображена структурная электрическая схема предлагаемого цифрового умно>кителя частоты.

10 Цифровой умножитель частоты содержит элемент ИЛИ 1, цифровую дифферснцнрующую цепь 2, состоящую из инвертора 3 и элемента И 4, линию задержки 5, цепь импульсной обратной связи, состоящую нз делителя

15 частоты 6 с переменным коэффициентом деления и элемента И 7. Выход линни задср ккп является выходом умножптеля.

Умножитель работает следующим образом.

Входной импульс подается на вход цпфро20 вой дифференцирующей цепи 2. Проднфференцированный импульс подается через элемент ИЛИ 1 на линию задержки 5 и на управляющий вход делителя 6. При этом делитель 6 устанавливается по выходу в единицу

25 и дает разрешение на прохождение импульсов с выхода линии задержки 5 через элемент И

7 импульсной обратной связи на второй вход элемента ИЛИ 1. Цикл работы длится до тех пор, пока делитель 6 не подсчитает число пм30 пульсов, равное его коэффициенту деления.

552688

После прихода Л -го импульса на вход делителя 6 (где N — число, равное коэффициенту деления дел ителя 6), последний разрывает цепь импульсной обратной связи, так как на его выходе появляется уровень логического нуля, и элемент И 7 запирается. При этом на выходе умножителя будет N импульсов.

При появлении следующего входного импульса цикл работы повторяется. Следовательно, предлагаемый умножитель выполняет роль умножителя частоты с переменным коэфф ициентом умножения. Коэффициент умножения определяется коэффициентом деления делителя 6, который в нем установлен.

Коэффициент деления делителя 6 может быть легко и просто изменен. Коэффициент умножения может быть сколь угодно большим и ограничивается только быстродейств ием элементной базы, т. е. быстродействием интегральных микросхем.

Формула изобретения

5 Цифровой умножитель частоты, содержащий делитель частоты с переменным коэффициентом деления, элементы И и последовательно соединенные дифференцирующую цепь, элемент ИЛИ и лин ию задержки, от10 л и ч а ю шийся тем, что, с целью упрощения умножителя, выход дифференцирующей цепи подключен к первому входу делителя частоты с переменным коэффициентом деления, выход которого через элемент И соединен с

15 вторым входом элемента ИЛИ, а вторые входы элемента И и делителя частоты с переменным коэффициентом деления объединены и подключены к выходу линии задержки.