Делитель частоты

Иллюстрации

Показать всеРеферат

О П И С А Н И Е п 552703

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 14.02.75 (21) 2105487/21 с присоединением заявки № (51) М. Кл,а Н ОЗК 23/00

ГосУдаРственный комитет (23) Пр и, Совета Министров СССР по делам изобретений и открытий (53) УДК 621.374.4 (088.8) Опубликовано 30.03.77. Бюллетень № 12

Дата опубликования описания 11.04.77 (72) Авторы изобретения

В. И. Родионов и Б. Ю. Каплан (71) Заявитель (54) ДЕЛИТЕЛЪ ЧАСТОТЫ

Изобретение относится к автоматике и может найти применение в счетчиках импульсов, временных (программных) устройствах и сумматорах.

Известен делитель частоты, содержащий два пересчетных устройства, управляемый триггер и логические элементы (1).

Однако такой делитель не достаточно надежен.

Наиболее близким техническим решением к изобретению является делитель частоты, содержащий и-разрядные пересчетные устройства, входы которых объединены и подключены к входному зажиму, и элемент ИЛИ 2.

Цель изобретения — повышение надежности работы делителя частоты.

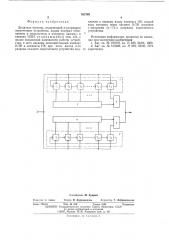

Это достигается тем, что в предлагаемый делитель частоты введены дополнительный элемент ИЛИ и элементы НЕ, при этом выход и-го разряда каждого пересчетного устройства подключен к первому входу элемента НЕ, второй вход которого через элемент ИЛИ соединен с выходами (n — 1)-х разрядов пересчетного устройства.

На чертеже представлена структурная электрическая схема делителя частоты.

11елитель частоты содержит два и-разрядных пересчетных устройства 1 и 2, (n — 1) разряды которых подключены к соответствующим элементам ИЛИ 3 и 4, два элемента НЕ 5 и

6, входы которых соединены с соответствующими выходами элементов ИЛИ и и-ми разрядами пересчетных устройств 1 и 2. Выходы элементов НЕ объединены и являются выхо дом делителя частоты.

В исправных пересчетных схемах 1 и 2 деление происходит синфазно и синхронно (поскольку цепь запуска у них общая), и импульсы с и-х разрядов через открытые элементы

НЕ 5, 6 поступают на выход делителя. При прекращении деления одним из пересчетных устройств сигналы на выходе делителя будут обеспечиваться другим пересчетным устройством.

В случае ложного срабатывания любого из

n — 1 разряда пересчетного устройства 1 сигналом элемента ИЛИ 3 будет закрыт элемент

НЕ 5, который не пропустит импульс и-ro разряда пересчетного устройства 1. На выходе

20 делителя частоты будут присутствовать только импульсы правильно работающего пересчетного устройства 2. Аналогично в случае сбоев в пересчетном устройстве 2 на выходе делителя частоты будут импульсы только пересчетного устройства 1.

Делитель выдает ложные импульсы только в случае одновременного выхода из строя пересчетных устройств 1, 2 вероятность чего значительно меньше, чем вероятность сбоя одного отдельно взятого пересчетного устройства.

552703

Формула изобретения

Составитель М. Аудринг

Техред И. Карандашова 1(орректор Т. Добровольская

Редактор С. Заика

Заказ 755/15 Изд. № 340 Тираж 1054 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, K-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Делитель частоты, содержащий и-разрядные пересчетные устройства, входы которых объединены и подключены к входному зажиму, и элемент ИЛИ, отличающийся тем, что, с целью повышения надежности работы устройства, в него введены дополнительный элемент

ИЛИ и элементы НЕ, при этом выход и-го разряда каждого пересчетного устройства под4 ключен к первому входу элемента НЕ, второй вход которого через элемент ИЛИ соединен с выходами (n — 1) -х разрядов пересчетного устройства.

Источники информации, принятые во внимание при экспертизе изобретения

1. Авт. св. № 197278, кл. Н ОЗК 23/04, 1966.

2. Авт. св. № 515289, кл. Н ОЗК 23/00, 1974

10 (прототип) .