Интегрирующее устройство

Иллюстрации

Показать всеРеферат

н

--оок-. :

ВВ,тем . ь о

О П И С А "Й И Е п 553629

Союз Советских

Социалистических

Республик

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 04.05.75 (21) 2131222/24 с присоединением заявки № (23) Приоритет

Опубликовано 05.04.77. Бюллетень № 13

Дата опубликования описания 03.06.77 (51) М. Кл. G 06G 7/18

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.335(088.8) (72) Авторы изобретения А. А. Джавадов, И. А. Набиев, М. М. Мустафаев и Ш.-М. P. Гейдаров (71) Заявитель Научно-исследовательский и проектный институт по комплексной автоматизации нефтяной и химической промышленности (54) ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной и информационно-измерительной технике и к системам централизованного контроля.

Из|вестны интегрирующие устройства, содержащие источник импульсов опорной частоты, счетчики импульсов и блок управления (1).

Недостатком известных устройств является их относительная сложность, Наиболее близким техническим решением к данному изобретению является интегрирующее устройство, .содержащее блок вычитания, первый вход которого подключен к источнику импульсов опорной частоты, а выход — к делителю частоты, последовательно с .которым включен счетчик импульсов, подсоединенный управляющим и нулевым входами к соответствующи vI выходам блока управления (2).

Известное интегрирующее устройство требует применения большого объема аппаратуры при необходимости интегрирования группы сигналов.

Целью изобретения является упрощение устройст ва.

Поставленная цель достигается тем, чпо устройство содержит три коммутатора, управляющие входы которых подключены к соответствующим .выходам блока управления, элемент «И», регистры сдвига,по числу интегрируемых сигналов, сумматор и преобразователь параллельного кода в последовательный, информационные входы которого подключены к соответствующим выходам счетчика импульсов, тактовый вход соединен с со ответствующим выходом блока управления, а выход — с первым входом сумматора, информационные входы первого коммутатора подключены к соответствую10 щим входам устройства, а его выход — ко второму входу блока вычитания, информационный вход второго коммутатора соединен с выходом сумматора, а выходы второго коммутатора через соответствующие регистры

15 сдвига подключены ко входам третьего коммутатора, выход которого соединен со вторым входом сумматора и с первым входом элемента «И», подключенного выходом к выходу устройства, второй вход элемента «И»

20 и сдвиговые входы регистров сдвига подсоединены к соответствующим выходам блока управления.

Такое устройство проще известного устройства.

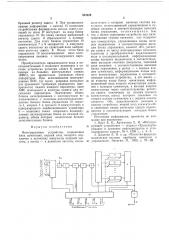

25 На чертеже приведена схема устройства.

Устройство содержит первый коммутатор

1, с помощью которого осуществляется коммутация той или иной частоты входной группы, блок вычитания 2, один вход которого

30 подключен к источнику опорной частоты f»

553629

/г

k,=

r где г (значение опорной частоты для всех параметров группы одинаковы и,соответствуют нулевому значению параметра) и с помощью которого вычитается опорная частота из входной частоты, управляемый делитель частоты 3, который осуществляет деление на соответствующий коэффициент, счетчик импульсов 4, где накапливаются импульсы с выхода делителя 3, преобразователь параллельного кода в последовательный код 5, сумматор,б, второй коммутатор 7, который коммутирует выход сумматора 6 ко входу соответствующего регистра сдвига 8, третий коммутатор 9, бло к управления 10 и элемент «И» 11, подсоединенный к выходу устройства 12, шины 13, 14, 15, 16, 17.

Групповое интегрирующее устройство работает следующим образом.

Импульсом «сброс» по шине 13 блок управления 10 приводится в исходное состояние. На выходе «сброс» 1 блока управления

10 формируется импульс, по которому счетчик 4 сбрасывается в нулевое состояние.

После этого на сдвиговые входы всех регистров сдвигов 8поступают импульсы сдвига с выхода блока управления 10. При этом коммутаторы 7 и 9 заперты и поэтому после поступления числа импульсов, равного числу разрядов одного регистра сдвига 8 (они все равны между собой), все регистры сдвига 8 приводятся в исходное нулевое состояние.

После этого по шине 14 на вход блока управления 10 поступает импульс «пуск», по которому устройство лереводится в циклический режим интегрирования, Циклический режим интегрирования начинается с подключением первой входной частоты (/) через коммутатор 1 ко входу, блока вычитания

2. Блок вычитания 2 осуществляет вычитание опорной частоты, значение которой соответствует нулевому значению параметра (например, для унифицированных частот4—

8 кгц значение опорной частоты равно

4 кгц) из входной. Импульсные последовательности, полученные из разности f (t)— — fo с выхода блока вычитания 2.начинают поступать на вход управляемого делителя 3 частоты. Коэффициенты деления делителя 3 задаются блоком управления 10 в соответствии с выбранным номером параметра.

Коэффициенты деления каждого пар а метра определяются соотношением — коэффициент, определяемый максимальным значением шкалы интегратора (соответствует коэффициенту в указанном прототипе); — коэффициент, определяемый отношением времени одного цикла

1ц к времени интегрирования т

З0

65 каждого параметра в одном цикле.

Далее импульсы с выхода делителя частоты

3 поступают на счетный;вход счетчика 4.

К концу:времени интегрирования т каждого цикла в счетчике 4 будет записано число, равное интегральному значению соответствующего параметра, в данном случае первого, за время одного цикла 1„. По истечении времени т для первого параметра блоком управления 10 формируются такты, которые начинают поступать на вход преобразователя параллельного кода в последовательный код 5 и на сдвиговый вход первого регистра сдвига

8. Одновременно при этом на управляющие входы коммутаторов 7 и 9 с выхода блока управления 10 поступают сигналы, с помощью которых выход первого регистра 8 подключается ко входу сумматора 6, а его выход — к информационному входу первого регистра сдвига 8. Коммутатор 1 при этом закрывается. Начиная с этого момента на оба входа одноразрядного комбинационного сумматора 6 поступают последовательные коды (если к этому времени в регистре сдвига 8 был нулевой код, то на второй вход сумматора 6 поступают нули). С помощью одноразрядного комбинационного сумматора б осуществляется сложение двух последовательных кодов, в данном случае интегрального значения первого параметра за один цикл (/ц) с нулевой информацией. Результат сложения через коммутатор 7 записывается в первый регистр сдвига 8. После формирования последнего импульса сдвига блоком управления 10 счетчик 4 сбрасывается в нулевое состояние и вновь коммутатор 1 открывается, а частота f () второго параметра подключается ко входу блока вычитания 2.

Коммутаторы 7 и 9 к этому времени закрываются. Интегрирование второго и остальных параметров протекает аналогично первому.

По окончании интегрирования последнего параметра группы цикл повторяется.

Когда истекает общее:время интегрирования одного из параметров группы, внешними устройствами формируются сигналы «чтение» и «Мю пар», которые по соответствующим шинам 15 и 16 поступают на входы блока управления 10. По этим сигналам блок управления

10 заканчивает операцию интегрирования текущего параметра в текущем цикле и останавливает процесс интегрирования. Блок управления находит регистр сдвига 8, номер которого соответствует номеру, поступающему по шине 16, открывает коммутаторы 7 и 9 и элемент «И» 11, а также закрывает коммутатор 1, Импульсы сдвига с выхода блока управления 10 поступают на сдвиговый вход выбранного регистра сдвига 8. Таким образом, последовательный код требуемой информации через открытый элемент «И» 11 поступает на выход 12 устройства. Одновременно эта информация через сумматор 6 и коммутатор 7 вновь перезаписывается в вы553629

Упдадпею цие сигноло бранный регистр сдвига 8. При правильном приеме информации с выхода 12 внешними устройствами формируется сигнал «квит», который по шине 17 поступает на вход блока управления 10. По этому сигналу выбранный регистр сдвига 8 сбрасывается в нулевое состояние. Для этого блоком управления 10 коммутаторы 7 и 9 запираются и импульсы сдвига поступают на сдвиговый вход выбранного регистра сдвига 8, После этого блок управления 10 восстанавливает цикл интегрирования начиная с последующего параметра.

Преобразователь параллельного кода в последовательный 5 позволяет применять в составе устройства регистры сдвига 8, выполненных на больших интегральных схемах (БИС), что значительно уменьшает объем аппаратуры. При использовании многоразрядных БИС, где число разрядов несколько раз превышает требуемую разрядность (дискретность) памяти каждого параметра, один

БИС используют в качестве памяти для нескольких параметров. Применение общих блоков интегрирования с многократным использованием с помощью дополнительно введенных блоков: блока управления 10, первого 1, второго 7 и третьего 9 коммутаторов и одноразрядного комбинационного сумматора

6 — позволяет также сокращать индивидуальные интегрирующие блоки на каждый параметр, объем которых значительно больше дополнительных блоков.

Формула изобретения

Интегрирующее устройство, содержащее блок вычитания, первый вход которого подключен к источнику импульсов опорной частоты, а выход — к делителю частоты, последовательно с которым включен счетчик импульсов, подсоединенный управляющим и нулевым входами к соответствующим выходам блока управления, о т л и ч а ю щ е е с я тем, 5 что, с целью упрощения устройства .при интегрировании группы сигналов, оно содержит три коммутатора, управляющие входы которых подключены к соответствующим выходам блока управления, элемент «И», регист10 ры сдвига по числу интегрируемых сигналов, сумматор и преобразователь параллельного кода в последовательный, информационные входы которого подключены к соответствующим выходам счетчика импульсов, тактовый

15 вход соединен с соответствующим выходом блока управления, а выход — с первым входом сумматора, информационные входы первого коммутатора подключены к соответствующим входам устройства, а его выход—

20 ко второму входу блока:вычитания, информационный вход второго коммутатора соединен с выходом сумматора, а выходы второго коммутатора через соответствующие регистры сдвига поключены ко входам третьего коммутатора, выход которого соединен со вторым входом сумматора и с первым входом элемента «И», подключенного выходом к выходу устройства, второй вход элемента «И» и сдвиговые входы регистров сдвига подсоединены к соответствующим выходам блока управления.

Источники информации, принятые во внимание при экспертизе:

1. Круг E. К., Артамонов Е. И. «ИнтегрпЗ5 рующее устройство» вЂ” журнал «Транспортирование и хранение нефтепродуктов и углеводородного сырья», Ко 4, 1969 г., с. 3 — 4.

2. Диденко К. Н. и др. «Частотно-ферродпнамическая система приборов контроля и

40 управления», Энергия, М., 1969, с. 79 — 88.