Накопитель для постоянного запоминающего устройства

Иллюстрации

Показать всеРеферат

Сак!з Советских

Социалистических

Республик

ОП ИСАНИ Е

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

«!553677 (61) Дополнительное к авт. свид-ву— (22) Заявлено 18.06.75 (21) 2146208/24 с присоединением заявки— (23) Приоритет— (43) Опубликовано 05.04.77. Бюллетень М 13 (45) Дата опубликования описания 25.07.77 (51) М. Кл.- G 11 С 5/12 государственный ко!иитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.327.66 (088.8) (72) Авторы изобретения

H. Н. Журавский и А. М. Селигей (71) Заявитель

Киевский ордена Трудового Красного Знамени завод электронных вычислительных и управляющих машин (54) НАКОГ1ИТЕЛЬ ДЛЯ ПОСТОЯHНОГО

ЗАПОМИНАтОЩЕГО УСТРОЙСТВА

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в трансформаторных постоянных запоминающих устройствах (ПЗУ) .

Известны накопители для ПЗУ.

Один из известных накопителей содержит ячейки памяти, выполненные на двух сердечниках и двух диодах (1).

Наиболее близким техническим решением к данному изобретению является накопитель, который содержит ячейки памяти, выполненные на двух сердечниках и двух транзисторах. Первые сердечники всех ячеек памяти прошиты шинами записи «нуля», а вторые— шинами записи «единицы» (2).

Недостатком известных накопителей является сравнительно большая индуктивность обмотки опроса, общей для двух сердечников„ и появление вслед за сигналом «нуля» выброса, имеющего ту же полярность, что и 20 сигнал «единицы». Это снижает быстродействие и надежность работы накопителя.

Целью изобретения является повышение быстродействия и надежности работы пако пителя.

Эта цель достигается тем, что в предложенном накопителе коллекторы ка;«дого второго транзистора ячеек памяти через резисторы подключены к источнику питания, а база второго транзистора соответственно к коллектору первого транзистора.

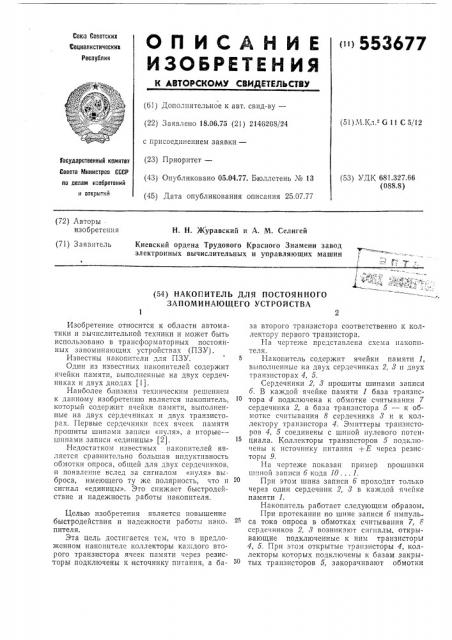

На чертеже представлена схема накопптеля.

Накопитель содержит ячейки памяти 1, выполненные на двух сердечниках 2, 8 и двух транзисторах 4, 5.

Сердечники 2, 8 прошиты шинами записи б. В каждой ячейке памяти 1 база транзистора 4 подключена к обмотке считывания 7 сердечника 2, а база транзистора 5 — к обмотке считывания 8 сер„8 и к коллектору транзистора 4. Эмиттеры транзисторов 4, 5 соединены с шиной нулевого потенциала. Коллекторы транзисторов 5 подключены к источнику питания +Е через резисторы 9.

На чертеже показан пример прошивки шиной записи б кода 10... 1.

При этом шина записи б проходит только через один сердечник 2, 8 в каждой ячейке памяти 1.

Накопитель работает следующим образом.

При протекании по шине записи б импуль са тока опроса в обмотках считывания 7, 8 сердечников 2, 8 возникают сигналы, открывающие подключенные к ним транзисторы

4, 5. При этом открытые транзисторы 4, коллекторы которых подключены к базам закрытых транзисторов 5, закорачивают обмотки

553677

Формула изобретения

15 б,1

Составитель В. Гордонова

Техред М. Семенов

Редактор Л. Утехина

Корректор В. Гутман

Заказ 443/1147 Изд. № 38 Тираж 769 Подписно

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент» считывания 8, что исключает возможность появления в этих разрядах помех «нуля» и возникновение колебательных процессов. С коллекторов открытых транзисторов 5, подключенных к резисторам 9, снимаются считанные сигналы «единиц».

В предложенном накопителе для ПЗУ при чтении из него информации обеспечивается закорачивание обмоток считывания сердечников тех разрядов, в которых записаны

«нули».

Это существенно повышает быстродействие и надежность накопителя.

Накопитель для постоянного запоминающего устройства, содержащий ячейки памяти, выполненные на двух сердечниках и двух транзисторах, при этом первые сердечники всех ячеек памяти прошиты шинами записи

«нуля», а вторые — шинами записи «единицы», базы первых транзисторов ячеек памяти подключены к обмоткам считывания соответствующих сердечников, а эмиттеры соединены с шиной нулевого потенциала, базы

5 вторых транзисторов всех ячеек памяти подключены к обмоткам считывания соответствующих вторых сердечников, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия и надежности накопителя, коллекторы

1О каждого второго транзистора ячеек памяти через резисторы подключены к источнику питания, а база второго транзистора подключена соответственно к коллектору первого транзистора.

Источники информации, принятые во внимание п ри экспертизе:

1. Крайзмер Л. П. Устройства хранения дискретной информации, изд-во «Энергия», 20 1969 г.

2. Брик Е. А. «Техника ПЗУ», М., изд-во

«Сов. радио», 1973 r., стр. 112.