Логический запоминающий блок

Иллюстрации

Показать всеРеферат

Col03 Советснии

Социалистических

Республик

ОП ИС

ИЗОБРЕ

К АВТОРСКОМУ (61) Дополнительное к (22) Заявлено 15.07.75

M. Кл.е G 11 С 15/00 с присоединением зая (23) Приоритет (43) Опубликовано 05. (4б) Дата опубликова

Госудерстееиный комитет

Совете Министров СССР по делам изобретений и открытий

) УДК, 681.327.6 (088 8) (72) Авторы изобретения

Е. П. Балашов, М. С. Куприянов и Г, A. Петров (71) Заявитель

Ленинградский ордена Ленина электротехнический институт нм. 8. И. Ульянова (Ленина) (54) ЛОГИЧЕСКИЙ ЗАПОМИНАЮЩИЙ БЛОК

Изобретение относится к области запоминающих устройств (ЗУ) и может быть использовано при построении систем хранения и переработки информации, в частности информационно-поисковых систем.

Известны логические запоминающие блоки (1), (2).

Один из известных логических запоминающих блоков содержит двоичньй элемент памяти, адресную и разрядные шины (1). Этот блок используется при построении логических ЗУ, а также ассоциативных устройств.

Однако функциональные возможности этого блока ограничены, Наиболее близким техническим решением к данному изобретению является логический запоминающий блок, содержащий два элемента памяти, выходы первого из которых подключены к одним входам двух элементов И первой группы, друтие входы которых соединены с одной из управляющих шии, а выходы — со входами второго элемента памяти, выходы которого подключены к одним входам двух элементов И второй группы, выходы которых соединены со входами первого элемента памяти. Другие входы элементов И второй группы подключены к выходам двух элементов И третьей группы, одни входы которых соединены с разрядными шинами (2) .

При использовании этого блока в логических ЗУ или ассоциативных ЗУ осуществляется реализация логических операций, а также ассоциативный поиск информации по совпадению (несовпадению) .

Однако этот блок не позволяет выполнять в

1р нем операции сложного ассоциативного поиска, такие как "больше чем", "больше или равно", "меньше чем" и т.д. Это значительно сужает область применения блока.

Целью изобретения является расширение об15 ласти применения логического запоминающего блока.

Указанная цель достигается тем, что предложенный блок содержит дополнительные элементы И, элемент ИЛИ и элемент"Запрет", инверсньй вход

20 которого подключен к одной из управляющих шин и одному входу первого дополнительного элемента И, прямой вход — к адресной шине и другому входу первого дополнительного элемента И, выход которого соединен с другими входами элементов И третьей группы, выход элемента "Запрет" подклю553681

15

25

35

50

55 чен к одним входам второго и третьего дополнительных элементов И, другие входы которых подключены к разрядным шинам, а выходы — ко входам второго элемента памяти, выходы которого соединены с одними входами четвертого и пятого дополнительных элементов И. Один вход шестого дополнительного элемента И подключен к адресной шине, другой — к одной из управляющих шин, а выход — к другим входам четвертого и пятого дополнительных элементов И, выходы которых соединены с разрядными шинами. Инверсный выход второго элемента памяти подключен к одному входу седьмого дополнительного элемента И, другой вход которого соединен с одной из управляющих шин, а выход — с одним входом элемецта ИЛИ, другой вход которого подключен к прямому выходу первого элемента памяти, а выход — к выходной шине. Прямой выход второго элемента памяти подключен к одному входу восьмого дополнительного элемента И, другой вход которого соединен с одной из управляющих шин, а выход — с одним из входов первого элемента памяти, Это позволяет выполнять операции сложного ассоциативного поиска, что существенно расширяет область применения логического запоминающего блока.

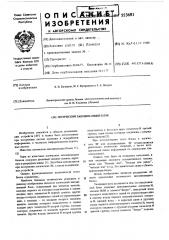

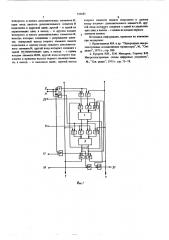

На фиг. 1 изображена функциональная схема логического запоминающего блока; на фиг, 2 структурная схема логического ЗУ с использованием логического запоминающего блока.

Логический запоминающий блок содержит два элемента памяти 1 и 2. Выходы первого элемента 1 подключены к одним иэ входов двух элементов И

3 первой группы, другие входы которых соединены с управляющей шиной 4, служащей для синхронизации. Выходы элемента памяти 2 подключены к одним входам двух элементов И 5 второй группы, другие входы которых соединены с выходами элементов И 6 третьей группы, одни входы которых соединены с разрядными шинами 7.

Один иэ входов первого дополнительного элемента И 8 соединен с управляющей шиной 9 и инверсным входом элемента "Запрет" 10, прямой вход которого и другой вход элемента И 8 соединены с адресной шиной 11. Выход элемента 8 соединен с другими входами элементов И 6. Выход элемента "Запрет" 10 подключен к одним входам второго 12 и третьего 13 дополнительных элементов И, другие входы которых подключены к шинам 7, а выходы — ко входам второго элемента памяти 2, выходы которого соединены с одними входами четвертого 14 и пятого 15 дополнительных элементов И. Один вход шестого дополнительного элемента И 16 подключен к шине 11, другой — к управляющей шине 17, служащей для считывания, а выход — к другим входам элементов И 15 и 14, выходы которых соединены с шинами 7. Инверсный выход элемента памяти 2 подключен к одному входу седьмого дополнительного элемента 18, другой вход которого соединен с управляюгцей ши4 ной 19, служащей для сравнения, а выход — с одним входом элемента ИЛИ 20, другой вход которого подключен к прямому выходу первого элемента памяти 1, а выход — к выходной шине 21. Прямой выход элемента памяти 2 подключен к одному входу восьмого дополнительного элемента И 22, другой вход которого соединен с управляющей шиной 23, а выход — с одним из входов элемента памяти 1.

Логическое ЗУ содержит (фиг. 2) управляющие блоки 24, одни входы которых соединены с настроечными шинами 25,.а другие — с выходами регистра входного слова 26. Адресные шины логических запоминающих блоков, образующих накопитель логического ЗУ, подключены к соответствующим выходам регистра адреса 27.

Рассмотрим работу логического запоминающего блока при записи и считывании информации, реализации элементарных логических операций, а также операш и простого и сложного поисков.

Управляющие блоки 24 функционируют также как и в обычном логическом ЗУ.

Запись информации в логический запоминающий блок может производиться как в элементы памяти 1, так и в элементы памяти 2. В первом случае устанавливается в единичное состояние соответствующий разряд регистра адреса 2, и подается сигнал на управляющую шину 9. Входное слово х (х, х,..., хп) с разрядных шин 7 записывается через элементы И 5 и 6 в элемент памяти 1. Во втором случае сигнал на управляющую шину 9 не подается. В результате на выходе элемента "Запрет"

10 возникает сигнал, поступающий на элементы И 12 и 13, поэтому входное слово Х с разрядных шин 7 записываетсЯ в элемент памяти 2.

Для считывания информации в единичное состояние устанавливается соответствующий разряд регистра адреса 27, и подается сигнал на шину 17, В результате на выходе элемента И 16 возникает сигнал, поступаюгций на элементы И 14 и 15 и информация с выходов элемента памяти 2 поступает на шины 7. При хранении информации в элементах памяти 1 подается сигнал на шину 4. В результате информация переписывается в элементы памяти 2, а потом производится считывание.

Выполнение элементарных логических операций (дизъюнкции, конъюнкции, запрета и дф. в режиме записи информации в элементы памяти 1 или 2 производится так же, как и в известном логичес. ком запоминающем блоке (11.

Реализуя логическую операцию неравнозначности или равнозначности между входным словом х (x> хг,."> хо) и любым словом устройства у ° (y у ..., у ). или целым массивом слов, 32 " Зп можно производить простой поиск информации.

Для этого набор сигналов подается на настроечные шины 25, соответствующий, например, операции неравнозначности, устанавливаются в единичное состояние соответствующие разряды регистра адреса 27 и подается сигнал на управляющую шину 9. В

553(»81

50 (х;9у ;) Ох, =у„;

1-ом разряде j-го слова массива реализуется операция неравнозначности

7.; =х;eу i =(x у;ч х; Y,)

Результат операции получается в элементе памяти 1. При подаче сигнала на шину 4 результат операции переписывается в элемент памяти 2, и единичный сигнал на одной из прямых разрядных шин 7 при считывании результата операции свидетельствует о несовпадении входного слова и слова, хранящегося в данной числовой линейке. Для восстановления исходной информации производится повторно операция неравнозначности

Выполнение операций сложного поиска рассмотрим на примере сравнения информации по числовому критерию "больше чем". Для определения соотношения x; )yi; необходимо выполнить логическую операцию Z) =xjyjj Причем х )iу1 имеет место только в том случае, если выполняются соотношения

И <у)»

/ (х,vу. )=1, =1,и. .8=- +1

Из этих выражении следует, что для определеii ния соотношения х ) yj необходимо иметь цепочку переносов" для анализа значений х; и у11 в каждом из разрядов кодов х и у1. Данную цепочку образуют последовательно соелинепные элементы И 18 и ИЛИ 20. Операция сравнения информации по числовомукритерию "больше чем" производится следую»цим образом.

1) в исходном состоянии элементы памяти 1 и 2 хранят -значение y11., 2) в элементе памяти 1 реализуется логическая операция xjyij, результат которой с прямого выхода элемента памяти 1 поступает на один из входов элемента ИЛИ 20.

3) в элементе памяти 2 реализуется логическая операция xjyjj, и с инверсного выхода снимается результат логической операпни xjó)j = хjvy1j который подается на оди»гиз входов элемента И 18;

4) подается сигнал на шину 17, и сигнал на шине 21 свидетельствует о в»лполнении условия х )

) у1, а его отсутствие — о выполнении условия х(у1.

Рассмотренная операция сравнения информации по числовому критерию больше чем" может быть выполнена одновременно над всем объемом хранимой в устройстве информации. Результаты сравнения фиксируются на шинах 21.

Для восстановления исходной информации необходимо сложить результаты логических операций,полученных в элементах памяти 1 и 2, и произвести операцию неравнозначности х, у „v х, ) „х, (- f <, 6

Это осуществляется при подаче сигнала на шину 23, вследствие чего результат логической операции х1у1, поступает на единичный вход элемента памяти 1, т.е. происходит логическое сложение с

РезУльтатом логической опеРации xj Yi j П сле этого

5 подается сигнал на шину 4,и полученная логическая сумма переписывается в элемент памяти 2. Операция неравнозначности производится так же как было рассмотрено выше.

Следует отметить, что рассмотренные операции, выполняемые блоком, не исчерпывают его функциональных возможностей. В нем эффективно выполняется логическая обработка массивов информации: логическое сложение, умножение, инвертирование матриц, упорядочение информации. Логи15 ро ческое сложение массивов бьпш уже использовано при выполнении операции сравнения llo числовому критерию "больше чем".

Рассмотрим в качестве прил<ера логическое умножение массивов информации. Конъюнкния од20 поименных элементов массивов информ мании можно дрддсдзвдть в ддедувшем ниде:

=д.;д у, д;;ду

Следовательно для реализации логического умножения двух массивов информации необходимо в элеме»пы памяти 1 и 2 записать инверсные значения элементов, сло)ьмть их, и полученную сул|му проинвертировать. Инвертирование производится лри подаче определенного набора управляющих сигналов на настроечные шины 25.

Формула изобретения

Логический запоминающий блок, содержащии два элемента памяти, выходы первого из которых подключены к одним входам двух элел<енто вИ первой группы, другие входы которых соединены с одной из управляющих шин, а выходы — co входами второго элемента памяти. выходы которого подключены к однил» входам двух элементо вИ второй группы, выходы которых соединены со входами первого элемента памяти, другие входы элементов И второй группы подключены к выходам двух элементов И третьей группы, одни входы которых соединены с разрядными шиналш, о т л ич а ю ш и и с я тем, что, с целью расширения области применения б)<ока, он содержит дополнительные

1i элементы И, элеменг ИЛИ в элемент Запрет, инверсный вход которого подключен к однои из управляющих ивин и одному входу первого дополнительного элемента И, прямой вход — к адреснои шине и другому входу первого дополнительного элемента И, выход которого соединен с друтими входами элементов И третьей группы; выход элемента Запрет" полключен к однил< входам второго и третьего дополнительных элементов И. другие входы которых подключены к разрядным шинам, а выходы — ко входам второго элел<ента памяти, выходы которо»» соединены с одними входами

553681

19

7 четвертого и пятого дополнительных элементов И, один вход шестого дополнительного элемента И подключен к адресной шине, другой — к одной из управляющих шин, а выход — к друтим входам четвертого и пятого дополнительных элементов И, выходы которых соединены с разрядными шинами; инверсный выход второго элемента памяти подключен к одному входу седьмого дополнительного элемента И, другой вход которого соединен с одной изуправляннцих шин, а выход — с одним входом элемента ИЛИ, другой вход которого подключен к прямому выходу первого элемента памяти, а выход —. к выходнои шине; прямой выход

8 второго элемента памяти подключен к одному входу восьмого дополнительного элемента И, другой вход, которого соединен с одной из управляющих шин, а выход — с одним иэ входов первого элемента памяти.

Источники информации, принятые во внимание при экспертизе:

1. Прангишвили И.В. и др. "Однородные микроэлектронные ассоциативные процессоры", М., "Сов. радио", 1973 r., стр. 280.

2. Букреев И.Н., Б.М. Мансуров, Горячев В.И.

Микроэлектронные схемы цифровых устройств", М., "Сов. радио", 1975 г. стр. 73 — 78.