Логическое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

>553682

Союз Советских

Социалистических

Республик,."+, . . h,,, г =(61) Дополнительное к авт. свид-ву— (22) Заявлено 13.01.76 (21) 2315158/24 с присоединением заявки— (23) Приоритет— (43) Опубликовано 05.04.77. Бюллетень ¹ 13 (45) Дата опубликования описания 25.07.77 (51) Ч.Кл.-" С 11 С 15/00

Государственный комитет

Совета Министров СССР по делам изобретений н открытий (53) УДК 628.327.6 (088.8) (72) Авторы изобретения Е. П. Балашов, А. 10 Гордонов, Н. В. Ерхова, Е. В. Коленов, Г. А. Петров, В. С. Степанов и Ю. А. Суровцев (71) Заявители (54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области запоминающих устройств и может быть применено в системах хранения и обработки информациии.

В настоящее время особое значение приобретают задачи увеличения помехоустойчивости, повышения достоверности передачи и обработки информации. Одним из методов решения этих задач является применение помехоустойчивых кодов в сочетании с синхронной передачей информации.

Известны логические устройства, позволяющие производить фазирование по циклам с непрерывной передачей сообщений (1).

В этих устройствах фазирующие символы передаются в течение передачи m кодовых комбинаций. Датчик фазирующей комбина ции, подключенный к одному из «контактов» передающего распределителя, за каждый цикл передает элемент фазирующей комбинации на приеме, к соответствующему «контакту» распределителя подключается дешифратор фазирующей комбинации, выход которого соединяется с устройством управления. При таком способе фазирования может потребоваться (2т — 1) циклов. Поэтому, если в течение 2m циклов с выхода дешифратора не поступит импульс, то под действием устройства управления фаза приемного распределителя смещается на один «контакт» и процесс поиска фазирующей комбинации продолжается. Такой режим сохраняется до тех пор, пока дешифратор не зафиксирует наличие фазирующей комбинации. Под действием импульса с дешифратора триггер переходит в состояние «1», блокируя устройство управления.

Наиболее близким техническим решением к данному изобретению являются логические устройства, содержащие последовательно соединенные регистр и дешифратор адреса и и-разрядный блок памяти, регистр слова, подключенный к блоку управления и блоку анализа содержимого регистра слова, шины управления (2).

Недостатком данной схемы является небольшая скорость обработки информации, кодирования, декодирования и невозможность выполнения синхронизации по циклам.

Целью изобретения является расширение функциональных возможностей ЛЗУ для применения их при синхронизации по циклам.

Поставленная цель достигается тем, что предложение ЛЗУ содержит элементы И и

ИЛИ и дополнительный дешифратор адреса, один вход которого подключен к шине управления, а другие входы — к соответствующим выходам регистра адреса и через первую группу элементов И к первым входам элементов ИЛИ первой группы. Выходы эле563682

6О

65 ментов ИЛИ первой группы подключены и первым входам первой группы элементов регистра слова. Первый вход последнего элемент регистра слова через последовательно соединенные элементы ИЛИ и И подключен к соответствующему выходу и- разрядного блока памяти. Второй вход элемента И подключен к шине управления. Вторые входы элементов ИЛИ первой группы, первые входы второй группы элементов регистра слова и второй вход элемента ИЛИ подключены к соответствующим элементам И второй группы. Первые входы элементов И второй группы подключены к соответствующей шине управления, а вторые — к соответствующим выходам и-разрядного блока памяти, Вторые входы регистра слова через третью группу элементов И подключены к соответствующим выходам и-разрядного блока памяти. Вторые входы элементов И третьей группы подключены к соответствующей шине управления.

Выходы регистра слова подключены к соот ветствующим входам блока анализа содержимого регистра слова, другие входы которого подключены к шинам управления. Выходы первой группы элементов регистра слова через последовательно соединенные элементы И четвертой группы и ИЛИ второй группы подключены к входам регистра адреса, а вторые входы элементов ИЛИ второй группы через элементы И пятой группы и вторые входы элементов И четвертой группы подключены к соответствующим шипам управления. Выход первого элемента регистра слова подключен через последовательно соединенные элементы И и ИЛИ к соответствующему входу регистра адреса, а вторые входы элементов И и ИЛИ вЂ” к соответствующим шинам управления.

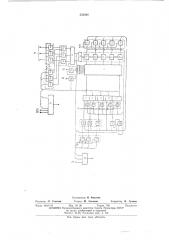

На чертеже изображена схема предлагаемого ЛЗУ.

Оно содержит элементы И второй группы

1 для прямого чтения, и-разрядный блок памяти 2, дешифратор адреса 8, регистр адреса 4, элементы ИЛИ второй группы 5, элементы И пятой группы 6 для приема кода адреса на регистр адреса из внешних устройств, блок управления 7, элемент ИЛИ 8, элементы И четвертой группы 9 для передачи на регистр адреса кода из регистра слова, элемент И 10 для передачи содержимого первого разряда регистра слова на вход регистра адреса, регистр слова 11, блок анализа содержимого регистра слова 12, элементы

И третьей группы 18 для выполнения суммирования по модулю два, элементы ИЛИ первой группы 14, элемент ИЛИ 15, элеменг

И 16 для чтения из первого разряда блока памяти в и-й разряд регистра слова, элементы И первой группы 17 для передачи кода адреса на регистр слова, дополнительный дешифратор адреса 18, шины управления

19 — 89.

Входы блока памяти 2 соединены с выходом дешифратора адреса 8, входы которого подключены к соответствующим выхода м регистра адреса 4, каждый вход которого подключен к соответствующему выходу элементов ИЛИ второй группы 5. Первые входы этих элементов подключены к соответствующему элементу И пятой группы 6, предназначенного для приема кода адреса из внешнего устройства. Первые входы элементов И пятой группы 6 подключены к шине управления «приема кода адреса» 80, а вторыс входы — к входным шинам 81. Вторые входы элементов ИЛИ второй группы 5 подклю чены к соответствующим элементам И четвертой группы 9, предназначенной для передачи кода адреса из регистра слова 11, первые входы элементов И четвертой группы 9 подключены к шине «передача кода из реги стра слова» 29, а вторые входы — к соответ ствующим выходам первой группы элементов регистра слова ll. Второй вход первого разряда регистра адреса 4 подключен к выходу элемента ИЛИ 8, первый вход которого подключен к шине управления «установка регистра адреса в следующее состояние» 82, второй вход подключен к элементу И 10 пере-. дачи содержимого первого разряда регистра слова на вход первого разряда регистра anреса 4, первый вход которого подключен к шине управления передачей 88, а второй вход — к выходу первого разряда регистра слова. Вторые входы каждого разряда блока памяти 2 подключены к блоку управления 7, первые входы которого подключены к управляющим шинам 20 — 28. Вторые входы блока

7 подключены к выходам регистра слова II.

Выходы регистра слова 11 подключены к входам блока анализа состояния регистра слова 12, вторые входы которого, подключены к шине «анализ состояния регистра слова» 85, а третьи входы — к шине «анализ состояния первого разряда» 86. Первые входы первой группы элементов регистра слова 11 подключены к соответствующим выходам элементов

ИЛИ первой группы 14, первые входы которых подключены к соотве1ствующему эле. менту И первой группы 17, предназначенного для передачи кода адреса на регистр слова.

Первые входы элементов И первой группьi

17 подключены к шине управления «передача кода адреса на регистр слова» 88, а вторые — к соответствующим выходам регистра адреса 4, которые одновременно подключены к дополнительному дешифратору адреса 18, другой вход которого подключен к шине управления опроса дешифратара 89. Первый вход последнего элемента регистра слова 11 подключен к выходу элемента И 15, первый вход которого подключен к элементу И 16, предназначенного для чтения первого разряда блока памяти íà и-й разряд регистра сло. ва. Первый вход элемента И 16 подключен к шине управления чтением из первого разряда блока памяти на соответствующий разряд регистра слова 87, а второй — к выходу первого разряда блока памяти 2. Вторые

553682 входы элементов ИЛИ первой группы 14, первые входы второй группы элементов регистра слова 11 и второй вход элемента ИЛИ

15 подключены к соответствующим элементам И второй группы 1, предназначенным для прямого чтения. Первые входы этих эле. ментов подключены к шине управления «прямого чтения» 19, а вторые — к соответствующим выходам элементов блока памяти 2.

Вторые входы элементов регистра слова 11 подключены к соответствующим элементам

И третьей группы 17, предназначенным для суммирования по модулю два. Первые входы этих элементов подключены к шине управления «сумма по модулю два» 84, а вто рые входы — к выходу соответствующих элементов блока памяти 2.

ЛЗУ может выполнять операции синхро. низации по циклам, циклическое кодирование, декодирование, левый логический сдвиг, правый логический сдвиг, прямую запись, прямое считывание и т. д.

В качестве примера рассмотрим реализацию операции «передача кода адреса на регистр слова». В исходном состоянии на регистре адреса 4 хранится операнд Х, «адрес ячейки А; и-разрядного блока памяти 2».

При подаче управляющего сигнала на шину управления «передачей кода на регистр сло ва» 88 сигнал поступает на элементы И первой группы 17. При этом информационные сигналы с выходов регистра адреса 4 через элементы И первой группы 17 и элементы

ИЛИ первой группы 14 поступают на входы регистра слова 11, записывая код операнда

Х на регистр слова.

Формула изобретения

Логическое запоминающее устройство, содержащее последовательно соединенные ре гистр, дешифратор адреса и и-разрядный блок памяти, регистр слова, подключенный к блоку управления и блоку анализа содержимого регистра слова, шины управления, отличающееся тем, что, с целью расширения функциональных возможностей устройства, оно содержит элементы И и ИЛИ и дополнительный дешифратор адреса, один вход которого подключен к шине управления, а другие входы — к соответствующим выходам регистра адреса и через первую группу элементов И к первым входам элементов ИЛИ пе рвой группы; выходы элементов ИЛИ первой группы подключены к первым входам первой группы элементов регистра слова; первый вход последнего элемента регистра слова через последовательно соединенные элементы ИЛИ и И подключен к соответствующему выходу и-разрядного бло

«а памяти; второй вход элемента И подключен к шине управления; вторые входы элементов ИЛИ первой группы, первые входы второй группы элементов регистра слова и второй вход элемента ИЛИ подключены к соответствующим элементам И второй группы; первые входы элементов И второй группы подключены к соответствующей шине уп. равления, а вторые — к соответствующим выходам и-разрядного блока памяти; вторые входы регистра слова через третью группу элементов И подключены к соответствующим выходам и-разрядного блока памяти; вторые входы элементов И третьей группы подключены к соответствующей шине управления: выходы регистра слова подключены к соответствующим входам блока анализа содержимого регистра слова, другие входы которого подключены к шинам управления; выходы первой группы элементов регистра слова через последовательно соединенные элементы И четвертой группы и ИЛИ второй группы подключены к входам регистра адреса, а вторые входы элементов ИЛИ второй группы через элементы И пятой группы и вторые входы элементов И четвертой группы подключены к соответствующим шинам управления; выход первого элемента регистра слова подключен через последовательно соединенные элементы И и ИЛИ к соответству40 ющему входу регистра адреса, а вторые входы элементов И и ИЛИ вЂ” к соответствующим шинам управления.

Источники информации, принятые во вни4> мание при экспертизе изобретения:

1. Стифлер Дж. Дж. Теория синхронной связи. Изд. «Связь», М., 1975 г.

2. Авторское свидетельство по заявке

М 2113б48/24, кл. G 11 С 15/00, 14.03.1975 г. (прототип).

533682

Составитель И. Фролова

Техред М. Семенов

Корректор В. Гутман

Редактор Л. Утехина

Тип. Харьк. фил. пред, «Патент»

Заказ 443/1147 Изд. № 38 Тираж 769 Подписi ое

ЦНИИПИ Государственного комитета Совета Министров СССР по де.(ам изобретений и открытий

Москва, )K-35, Раушская наб., д. 4/5