Устройство для хранения и выборки информации

Иллюстрации

Показать всеРеферат

п 553685

ОПИСАН И Е

ИЗОбРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сове Советских

Соииаиистических ресочбдик (б1) Дополнительное к авт. свид-ву (22) Заявлено 02.06.75 (21) 2139684/24 с присоединением заявки № (23) Приоритет

Опубликовано 05.04.77. Бюллетень № 13

Дата опубликования описания 14.04.77 (51) М. Кл. G 11С 27/02

Государственный комитет

Совета министров СССР (53) УДК, 681.327.66 (088.8) по аелам изобретений и открытий (72) Авторы изобретения

Г. Д. Бахтиаров и П. А. Дзарданов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ХРАНЕНИЯ И ВЫБОРКИ

ИНФОРМАЦИИ

Изобретение относится к области аналогоцифровой техники, а также области радиотехники, использующей дискретные методы обработки сигналов, и предназначено для дискретизации непрерывных сигналов. Оно может найти применение при построении аналогоцифровых преобразователей и при согласовании аналоговых и цифровых устройств в различных системах обработки сигналов.

Известно устройство выборки и запоминания (1), содержащее последовательный аналоговый ключ на биполярном транзисторе. Известно также устройство выборки и запоминания (2), содержащее последовательный ключ на полевом транзисторе.

Недостатком таких устройств выборки и запоминания является сравнительно высокий уровень пролезаний через паразитные параметры ключей, что ограничивает как точность их работы, так и достижимую частоту дискретизации.

Из известных устройств выборки и запоминания наиболее близким по технической сущности является устройство (3), содержащее

n — р — n-транзистор, база которого подключена ко входу устройства и через первый резистор к шине нулевого потенциала и к одной из обкладок конденсатора. Змиттер n — р — n-транзистора соединен через второй резистор с отрицательной шиной питания. Другая обкладка конденсатора подключена к выходу устройства и к коллектору первого р — и — р-транзистора, а через третий резистор к эмиттеру второго р — и — р-транзистора, база которого соединена

5 с коллектором третьего р — п — р-транзистора, коллекторы n — р — n-транзистора и второго р — и — р-транзистора подсоединены к шинам питания соответственно, четвертый резистор, шину напряжения смещения, шину стробиро10 вания и шину напряжения ограничения.

Недостатками прототипа являются: ограниченное быстродействие в режиме образования выборочного значения, обусловленное наличием ограничительного резистора и

15 использованием насыщенного параллельного ключа; ограниченная частота дискретизации, связанная с необходимостью полного разряда накопительного конденсатора сравнительно ма20 лым коллекторным током разрядного транзистора перед каждым новым стробом; наличие существенных погрешностей образования выборочных значений при работе на нарастающих участках входного сигнала, что

25 обусловлено работой выходного транзистора в режиме, близком к режиму пикового детектора и отнесением выборочных значений к моментам окончания стробов; униполярность схемы с точки зрения вход30 ного сигнала.

553685

Целью изобретения является повышение быстродействия устройства.

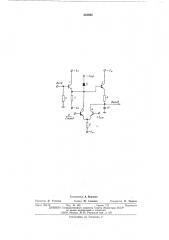

Эта цель достигается тем, что предложенное устройство содержит диод, анод которого подключен к эмиттеру и — р — n-транзистора, к базе второго р — и — р-транзистора и к коллектору третьего р — и — р-транзистора, эмиттер которого соединен с эмиттером первого р — n — ртранзистора и через четвертый резистор с положительной шиной питания. Базы третьего и первого р — и — р-транзисторов подключены к шине стробирующего импульса и шине напряжения смещения соответственно. Катод диода соединен с шиной напряжения ограничения.

На чертеже представлена принципиальная электрическая схема устройства.

Устройство содержит n — р — n-транзистор 1, р — и — р-транзисторы 2 — 4, диод 5, резисторы

6 — 9 и конденсатор 10.

Устройство работает в двух режимах: в режиме выборки, когда происходит образование выборочных значений сигнала на накопительном конденсаторе и в режиме хранения, когда образованное выборочное значение сигнала на конденсаторе поддерживается постоянным и используется для работы внешних устройств.

В режиме хранения потенциал на базе тран зистора 2 ниже потенциала источника Е,„„ подключенного к базе транзистора 4, на величину, достаточную для того, чтобы транзистор

2 был полностью открыт, а транзистор 4 полностью закрыт.

Сопротивление резистора 9 выбрано таким, что коллекторный ток транзистора 2 превосходит ток, протекающий через резистор 7. Потенциал Е„р выбран выше максимального (в данной схеме положительного) значения входного сигнала, что обеспечивает надежное запирание в рассматриваемом режиме транзисторов 1 и 3. Последнее обстоятельство обуславливает сохранение заряда, накопленного конденсатором 10.

В режиме образования выборочного значения сигнала положительный перепад на базе транзистора 2 приводит к переключению дифференциального каскада, образованного транзисторами 2 и 4. Это приводит к быстрому изменению потенциала на накопительном конденсаторе до текущего значения сигнала с дальнейшим точным отслеживанием последнего на выходе устройства в отличие от прототипа и повышает быстродействие устройства.

Выбор исходного смещения на базе транзистора 2 и соответствующего значения напряжения Е„р позволяет использовать предложенное устройство для работы с биполярными сигналами, что в прототипе невозможно.

Устройство имеет следующие основные параметры: частоту дискретизации до 10 Мгц; максимальную погрешность образования выборочных значений входного сигнала синусоидальной формы частотой (погрешность сле5 жения) до 5 мгц, не более 0,5/o, динамический диапазон входного сигнала

+- 2в; интервал стробирования не менее 25 нс; апертурную неопределенность — единицы нс. и С помощью прототипа можно получить максимальную частоту дискретизации порядка

0,5 мгц, при погрешности взятия выборочных значений сигнала с полосой 0,25 мгц, доходящей до 5 от масимального значения сиг15 нала.

Таким образом, предложенное устройство позволяет при одинаковых затратах получить точность работы, быстродействие на порядок выше, чем при использовании прототипа.

Формула изобретения

Устройство для хранения и выборки информации, содержащее n — р — n-транзистор, база

26 которого подключена ко входу устройства и через первый резистор к шине нулевого потенциала и к одной из обкладок конденсатора, эмиттер и — р — и-транзистора соединен через второй резистор с отрицательной шиной пита30 ния, другая обкладка конденсатора подключена к выходу устройства и к коллектору первого р — и — р-транзистора, а через третий резистор к эмиттеру второго р — n — р-транзистора, база которого соединена с коллектором третьB5 его р — n — p-транзистора, коллекторы n †р †птранзистора и второго р — и — р-транзистора подсоединены к шинам питания соответственно, четвертый резистор, шину напряжения смещения, шину стробирующего импульса и ши40 ну напряжения ограничения, о т л и ч а ю щ е ес я тем, что, с целью повышения быстродействия устройства, оно содержит диод, анод которого подключен к эмиттеру и — р — и-транзистора, к базе второго р — и — р-транзистора и к

45 коллектору третьего р — n — р-транзистора, эмиттер которого соединен с эмиттером первого р — n — р-транзистора и через четвертый резистор с положительной шиной питания; базы третьего и первого р — и — р-транзисторов подао ключены к шине стробирующего импульса и шине напряжения смещения соответственно; катод диода соединен с шиной напряжения ограничения.

Источники информации, принятые во внимаM ние при экспертизе изобретения:

1, «Электроника», № 6, 1964, стр. 33 — 36.

2. Патент США М 3474259, кл. 307 — 238, опубл. 1969 г.

3. «Приборы для научных исследований», 60 № 4, 1963 r., стр. 3 — 14 (прототип).

553685

Составитель А. Воронин

Техред М. Семенов

Редактор Л. Утехина

1(орректор О. Тюрина

Типография, пр. Сапунова, 2

Заказ 765718 Изд, М 495 Тираж 722 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, К-35, Раушская наб., д. 4/5