Устройство для синхронизации генераторов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (») gg3711 (61) Дополнительное к авт. свид-ву-— (22) Заявлено22.12.75 (21) 2303483/07 с присоединением заявки №вЂ” (51) М. Кл.

Н02 У 3! 42

Государственный комитет

Совета Министров СССР оо делам изооретеннй и открытий (23) Приоритет (43) Опубликовано05.04.77.Бюллетень № 13 (45) Дата опубликования описания16.07.77

P3) УДК621.316,729, (088,8) М, Б. Вандер, В. Н. Константинов„В. Н. Корнеев и А. Е. Марков (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ

ГЕНЕРАТОРОВ

1

Устройство синхронизации генераторов относится к технике включения синхронных генераторов на параллельную работу и может быть использовано при синхронизации генераторов переменного тока, в част- 5 .чости судовых синхронных генераторов.

Известны устройства синхронизации, например, в которых определение момента включения производится при определенной разности частот, разности фаз и разности 1р напряжений с постоянным временем или с постоянным углом опережения (1,21.

Однако эти устройства не обеспечивают необходимой точности включения.

Ближайшим аналогом является устройство}5 синхронизации генераторов (31, содержащее блок преобразования текущего значения разности фаз напряжений синхронизируемых генераторов в код, выходы которого подклю, чены ко входам цифрового решающего бло- 20 ка, который воздействует на автоматический выкл. ючатель и содержит блок памяти текушего значения кода разности фаэ, связанный с блоком вычисления приращения разности фаэ, выход которого подключен к 25 входу блока сравнения текушего и допустимого значения разности фаэ, выход которого подключен к выходу,цйфррвого решающего блока- по регулироцанию частоты, и блок вычисления времени опережения, выход которого подключен ко входу блока запрета по разности напряжений, другой вход которого подключен к выходу блока преобразования, а выходы один - к выходу цифрового решающего блока по регулированию напряжения, а второй - к выходу по включению автоматического выключателя.

Выше приведенное устройство решает алгоритм включения генераторов на параллельную работу путем сравнения в дискретные промежутки времени кода приращения разности фаз, умноженного на постоянный коэффициент, с кодом мгновенного значения разности фаз. Такой алгоритм позволяет определить время опережения с высокой точностью только при неизменной разности частот синхронизируемых генераторов, а при наличии углового ускорения, вызванного воздействием сигнала с блока уравнивания частот или ыабросом нагрузки в момент

553711 а4 =Ф и+ л+ mtz >

Полученные коды приращений поступают в блок 6 сравнения текущего и допустимо го значений приращения разности фаз, При превышении допустимого значения блоком

45 6 вырабатывается команда на уравнивание частот синхронизируемых генераторов - zf.

Одновременно с предыдущей операцией коды приращений разности фаз последовательно поступают в блок 7 вычисления

50 кода углового ускорения, в котором происходит вычисление вторых конечных разностей т и чп+ >

» > > >+2 >

Конечные разности первого и второго порядка вместе с соответствуюшими эна60 чениями кодов разности фаэ поступают з синхронизации, появляется угловая ошибка, которая будет тем больше, чем больше величина ускорения.

Пель изобретении - повышение точности включения генераторов на параллельную рабо у.

Указанная цель достигается тем, что в устройстве для синхронизации генераторов, содержащем блок преобразования текущего значения разности фаз напряженИЙ синхроня 0 зируемых генераторов в код, выходы которого подключены ко входам цифрового решаюmего блока, который воздействует на автоматический выключатель и содержит--блок- — —— цамяти текущего значения кода разности

> фаз, связанный с блоком вычисления приращения разности фаз, выход которого подключен к входу блока сравнения текущего и донустимого значений разности фаз, выход которого подключен к выходу цифрового решаю- 0 щего блока по регулированию частоты, и блок вычисления времени опережения, выход которого подключен ко входу блока запрета по разности напряжений, другой вход которого подключен к выходу блока преобразования, а выходы один - к выходу цифрового решающего блока. по регулированию напряжения, а второй — к выходу по включению автоматического выключателя, решающий блок снабжен блоком вычисления кода углового ускорения и блоком вычисления времени ожидания момента совпадения фаз, причем. входы блока вычисления кода угло-вого ускорения подключены соответстве апэ к выходу блока вычисления приращения раз- 35 ности фаз и к выходу блока сравнении текущего и допустимого значений разности фаз, а его выход подключен к одному из входов блока вычисления времени ожидания момента совпадения фаэ, другие входы которого подключены соответственно к выходу блока вычисления приращения разности фаз и к выходу блока памяти текущего значения разности фаз, а выход блока вычисления времени ожидания момента совпадения под-ключен к входу блока вычисления времени опережения.

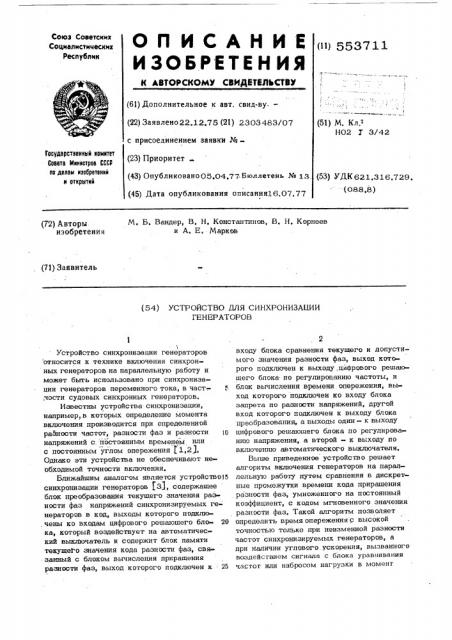

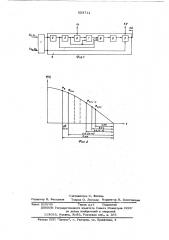

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - диаграмма, поясняющая работу устройства.

Выходы блока преобразования 1 подключены к синхронизируемым источникам.

Выход блока преобразования по разности фаз подключен к входу блока памяти 2, а выход по разности напряжений к входу 55 блока 3 запрета по разности напряжений цифрового решающего блока 4. Выход блока памяти подключен к входу блока

5 вычисления кода приращения разности фаз, выход которого подключен к входу блока 6 сравнения текущего и допустимого значений приращения разности фаз, вы ход которого, в свою очередь, подключен к выходу блока 4 по регулированию чаототы. Одновременно выход блока 5 подключен к входу блока 7 вычисления кода углового ускорения, выход которого подключен к входу блоку 8 вычисления време ни ожидания момента совпадения фаз. Выход блока 8 подключен к входу блока 9 вычисления времени опережения, выход ко торого подключен ко второму входу блока 3 запрета по разности напряжений, Выходы

--блока 3 подключены один - к выходу бло- ка 4 по регулированию напряжения, а вто рой - к выходу блока 4 управления авто- матическим выключателем.

Устройство работает следующим образом.

Напряжение синхронизируемых генератоpoB pIgI и дggg преобразуются с помощью блока преобразования 1. в код разности фаз Ч ..и, поступающий в блок памяти 2 и в код h О, пропорциональный разности напряжений, поступающий на вход блока 3 запрета по разности напряжений.

Измерение и запоминание кодов происходит в каждом периоде напряжений синхронизируемых генераторов, Таким образом, в блоке памяти 2 запоминается последо вательность дискретных значений кодов разности фаз: 9m, V +g........

Значения этих кодов последовательно поступают в блок 5, где производится вычисление приращений разности фаз за период измерения

> п = м и+ >

5537

Формула изобретения

35 в блок 8 вычисления времени ожидания момента совпадения фаз т - 1 /2 и кп г у

При этом, еслибы Ч г < О,то кривая, ха2, рактериэируюшая изменение разности фаз

- 7 . имеет вь1пуклость и поэтому выбирается наибольшой (с учетом знака) корень; и наоборот при ага„, 0кривая Ю1 вогну- тая и, соответственно, необходимо выбирать наименьший из двух корней.

Полученное значение 1 „,, времени ожидания поступает в блок 9 вычисления времени опережения, где происходит сравне- 15 ние этого значения с требуемым временем опережения tpn. Момент выдачи команды на.включение, определяется из условия

t„. -t „4 ht., к, оп 20 где А1 — шаг дискретности, Команда на включение проходит через блок

3 запрета по разности напряжений. В том случае, когда текущее значение разности напряжений превышает допустимое, вырабатывается команда на уравнивание напряжений -

6 числения приращения разности фаз, выход которого подключен к входу блока сравнения текущего и допустимого значений разности фаэ, выход которого подключен к выходу цифрового решающего блока по регулированию частоты, и блок вычисления времени опережения, выход которого подключен ко входу блока запрета по разности напряжений, другой вход которого подключен к в выходу блока преобразования, а выходы один — к выходу цифрового решающего блока по регулированию напряжения, а второй — к выходу по включению автоматического выключателя, о т л и ч а ю щ е ес я тем, что, с целью повышения точности включения генераторов на параллельную работу, цифровой решающий блок снабжен блоком вычисления кода углового ускорения и блоком вычисления времени ожидания момента совпадения фаэ, причемвходы блока вычисления кода углового ускорения подключены соответственно к выходу блока вычисления приращения разностифаз и к выходу блока сравнения текущего и допустимого значений разности фаз, его выход подключен к одному из входов блока вычисления времени ожидания момен,та совпаде пщ фаз, другие входы которого подключены соответственно к выходу бло ка вычисления приращения разности фаз и .к выходу блока памяти текущего значения разности фаз, а выход блока вычисления времени ожидания момента совпадения фаз подключен к входу блока вычисления времени опережения.

Устройство для синхронизации генераторов, содержащее блок преобразования текущего значения разности фаз напряжений синхронизируемых генераторов в код, выходы которого подключены ко. входам цифрового решающего блока, который воздействует на автоматический выключатель, и содержит блок памяти текущего значения кода разности фаз, связанный с блоком выИсточники информации, принятые во вни.мание при экспертизе:

1. Авторское свидетельство Мг 394890 кл. Н 02 j 3/42, 1971 r.

2. Авторское свидетельство о 416805, кл. Н 02 ) 3/ 42, 1971 г.

3. Авторское свидетельство по заявке

Л1 2063 1 27/07, кл. Н 02 3 3/42, 1 974 r.

553711

Составитель C. Фотина

Редактор В. Фельдман Техред О. Луговая, Кл)рректор: H. Золотовская

Заказ 210/40 Тираж g17 Подписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб., д. 3/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4